# *Test data reduction using LFSR reseeding technique in benchmark circuits*

R.KARTHICK<sup>1</sup>

Associate Professor,

Department of ECE,

Pondicherry Engineering College

rskarthick2003@yahoo.com

DR.V.SAMINADAN<sup>2</sup>,

Associate Professor,

Department of ECE,

Pondicherry Engineering College

saminadan@pec.edu

**Abstract-**Power dissipation during test is a significant problem as the size and complexity of systems-on-chip (SOCs) keep on to grow up. In scan shifting, more transitions occur in the flip-flops compared to what occurs during normal functional operation. This problem is further compounded when pseudorandom filling of the unassigned input values is engaged. Too much power dissipation during test can increase manufacturing costs by requiring the use of a more expensive chip packaging or causing unnecessary yield loss. In this project, a new test-data-compression scheme based on linear feedback shift register (LFSR) reseeding that significantly reduces power consumption during test is proposed. Test-data volume has also increased dramatically as the size and the complexity of chips grow. A large number of test pattern bits being assigned randomly cause a large number of transitions in the scan chains thereby increasing power dissipation during test drastically. To overcome this a new encoding algorithm is proposed to achieve test data compression without high test power.

**Keywords-**SOC, LFSR, Power Dissipation, Encoding algorithm.

## 1. INTRODUCTION

As the size and complexity of systems-on-a-chips (SOCs) continue to grow, the cost of VLSI test is increasing drastically. Larger chips require a larger amount of test data and dissipate a larger amount of power during test. Moreover, they are typically harder to test because they tend to have more hard-to-detect faults. Test time is a critical part of test cost and increases as the size and complexity of a chip increase. Reducing test cost is becoming an increasingly critical issue. This dissertation focuses on two important sources of the test cost, namely test data volume and test power. Test time depends on both test data volume and test power. Large test data volume increases test time because it requires more time to transfer the data to and from the chip.

Test power can slow down test speed, thereby increasing test time. If the average power Consumption during test is higher than the chip package's capability to dissipate heat the test must be run at a lower frequency. Therefore, both test power and test data should be considered to reduce test time effectively. Conventional test data compression schemes generally dissipate high power. Most conventional compression schemes exploit the fact that a test set has a large number of don't cares and only 1~5% of specified (care) bits. The don't cares are assigned to maximize compression. In this process, a large number of transitions may occur in test patterns. The

larger the number of transitions in the test patterns, the larger the power dissipation. This dissertation addresses these two important problems in the VLSI testing area, namely test data volume and test power.

### 1.1 TEST POWER VS. TEST DATA

Conventional test data compression schemes generally increase test power. Most conventional test data compression techniques are based on the fact that a large percentage of test set, typically 90%~95%, is filled with don't care bits. The don't care bits are assigned in a way that minimizes test data volume and not test power. To reduce the number of transitions in a chip during test, the don't care bits should be set to constant values.

Then, test power dissipation will be minimized, but the don't care bits would not be used for test data compression. On the other hand, if the don't care bits are used for test data compression, then the don't care bits cannot be used for test power reduction. For example, in linear feedback shift register (LFSR) reseeding scheme that is used in several commercial tools including Test compress by Mentor Graphics [02] and DBIST by Synopsys, the don't care bits are assigned almost randomly, which results in large power dissipation[11]. This is why test power can be a serious problem in test data compression techniques

### 1.2 LFSR RESEEDING

The basic idea in LFSR reseeding is to generate deterministic test cubes by expanding seeds. A seed was an first state of the LFSR that is lengthened by running the LFSR in self-governing mode. Since typically only 1-5% of the bits in a test vector are specified, most bits in a test cube do not need to be considered when a seed is computed because they are don't care bits. Therefore, the size of a seed is large amount smaller than the size of a test vector. Therefore, reseeding can considerably reduce test data storage and bandwidth [12]. Many test data compression schemes are based on LFSR reseeding. Causing high power dissipation. We present a new encoding scheme that can be used in Conjunction with any LFSR reseeding scheme to significantly reduce test power and even further reduce test storage.

R.Karthick, Dr.V.Saminadan

## 2. PROPOSED METHODOLOGY

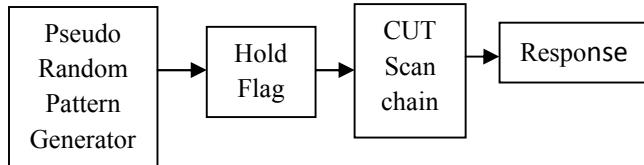

Fig 1. Basic Block Diagram

The proposed encoding scheme acts as a second stage of compression after LFSR reseeding. It accomplishes two goals. Initially, it decreases the number of transitions in the scan chains (by satisfying the undetermined bits in a changed mode), and second it reduces the number of specified bits that need to be generated via LFSR reseeding. The investigational results specify to facilitate the proposed method significantly reduces test power and in most cases provides greater test data compression than LFSR reseeding alone.

### 2.1. ENCODING ALGORITHM

Let a transition in a test cube be defined as a specified 0 (1) followed by zero or more X's followed by a specified 1 (0). The main thought of the planned encoding algorithm is to take advantage of the fact that number of transitions in a test cube is always less than the number of specified bits in a test cube. So, slightly using LFSR reseeding to directly encode the specified bits as in conventional LFSR reseeding, the future encoding algorithm segregates the test cube into blocks and only uses LFSR reseeding to generate the blocks that hold transitions. For the blocks that do not contain transitions, the logic value fed into the scan chain is simply held constant.

This method decreases the amount of transitions in the scan chains and in most cases also reduces the total number of specified bits that must be generated by the LFSR as compared with conventional LFSR reseeding

#### 2.1.1 Basic Concept

The future encoding scheme encodes each test cube with two kinds of data: hold flags and data bits. Every trial cube is divided into multiple blocks and each block has a one-bit hold flag. The hold flag indicates whether a transition occurs in a block.

There are three types of blocks:

##### 1) Transition block (Hold flag = 0)

One or more transitions exist in the block. Either both 0 and 1 are present in the block (e.g., XX1X0X), or only 0 or 1 is present but the last specified bit from a previous block was opposite.

##### 2) Non-transition block (Hold flag = 1)

No transition occurs in current block. Only 0 or 1 is present in the block, and the last specified bit from a previous block is same (e.g., X0XX0X).

##### 3) Don't care block (Hold flag = X)

No specified bits occur in the block, all are don't cares. If the hold flag for a block is 1, then the data bits in the block are simply held constant from the last data bit in the previous block. If the hold flag is 0, then the data bits are loaded directly from the LFSR. If the hold flag is X, then it can be either treated as a non-transition block or as a transition block with all X data. Both the hold flags and the data bits are generated from a single LFSR using reseeding.

Table 1. Example of encoding test data

| BLOCK    | BLOCK        | BLOCK        | BLOC<br>K | BLOCK      |

|----------|--------------|--------------|-----------|------------|

| Original | 0 X X<br>1   | X 1 1<br>1   | 1 X 1 X   | X X X<br>X |

| Encoded  | 0 0 X X<br>1 | 1 X 1 1<br>1 | 11X1 X    | X X X XX   |

An example of the proposed encoding is shown in Table 3.1. The test sequence in the example is composed of 4 blocks and each block has 1 hold flag and 4 data bits. The hold flags are shown in bold in the "Encoded" bit sequence row. The original test cube contains 7 specified bits. However, using the proposed encoding scheme, the encoded data has only 3 specified hold flags and 2 specified data bits giving a total of only 5 specified bits.

Table 2. Example of encoding test data

| BLOCK    | BLOCK        | BLOCK        | BLOCK       | BLOCK        |

|----------|--------------|--------------|-------------|--------------|

| Original | X 0 1<br>X   | X 0 X<br>0   | X X X<br>X  | 1 1 1<br>X   |

| Encoded  | 0 X 0 1<br>X | 1 X 0 X<br>0 | 0 XX X<br>1 | 1 1 1 1<br>X |

Thus, the proposed encoding scheme reduces the number of specified bits that need to be generated using LFSR reseeding. As shown in table2 the 1's in block 2 and block 3 don't need to be generated directly by the LFSR, but are rather generated as a by-product of the fact that the hold flags keep the input to the scan chain held constant at 1. Thus, test data compression can be achieved in this way.

Moreover, no transitions will occur when generating block 2 and block 3 because the hold flags are 1 thus keeping all the bits in the blocks constant. This would not be the case in conventional LFSR reseeding where the X's in blocks 1 and 2 get filled with random data which may results in many more transitions. Thus, a reduction in the number of transitions can be achieved in this way.

#### 2.1.2 Conversion Procedure

R.Karthick, Dr.V.Saminadan

It is possible to increase the number of non-transition blocks by converting some transitions blocks into non-transition blocks. There are two requirements that must be satisfied in order to convert a transition block into a non-transition block. The first is that it cannot contain both specified 0's and specified 1's. The second is that the last bit of the previous block must be an X. Two examples of this are shown in table 3.1.

Block 2 is initially a transition block even though it only contains specified 0's because the last specified bit in block 1 was a 1. However, the very last bit of block 1 is a don't care, so a conversion procedure can be used to specify that don't care as a 0 and thereby convert block 2 into a non-transition block. Even though this conversion required adding an extra specified data bit, the net result is still a reduction in the total number of specified bits because now block 2 is a non-transition block and thus none of its data bits need to be generated by the LFSR.

This same conversion procedure can also be used to convert block 4 in Table 1. In to a non-transition block. By increasing the number of non-transition blocks, the conversion procedure can help to reduce both test storage (since it can reduce the total number of specified bits) as well as test power (since it can reduce the number of transitions by enabling all the X's in the converted non-transition block to be filled with the same logic value Convert blocks 2 and 4 into non-transitions blocks).

Table 2. Example of conversion procedure (last bit of blocks 1 and 3 are specified to convert blocks 2 and 4 in to non-transitions blocks

### 2.1.3. Partitioning into Hold Cube Compatible Sets

The test storage for LFSR reseeding depends on the number of specified bits. For each block that is not a don't care block, the hold flag for that block is specified. If the number of specified hold flags becomes larger than the number of the specified test data bits that are reduced by using the proposed encoding scheme, then the encoding scheme would be reducing test power dissipation at the cost of test storage. The test storage would increase because the total number of specified data bits plus specified hold bits would exceed the total number of specified bits in the original test cubes. However, in this chapter, a method for reducing the number of specified hold flags is introduced. The key idea is to take advantage of the fact that many test cubes may have compatible assignments in their corresponding hold flags. We will denote the set of hold flags for one test cube as a hold cube since each hold flag can be either a 1, 0, or don't care (X). If several consecutive test cubes have the same hold cube, it is not necessary to change any of the hold flags. Thus, the hold flags could be loaded once and then reused when applying subsequent test cubes.

The hold cubes for a pair of test cubes are compatible if they do not conflict in any specified bit positions. In other words, for every bit position where one hold cube has a specified value, the other hold cube has either the same specified value or a don't care (and vice versa). Let a hold cube compatible set be defined as a set of test cubes with mutually compatible hold cubes. Since typically only around 1-5% of the data bits in a test cube are specified, the corresponding hold cube will typically have a large number of don't cares

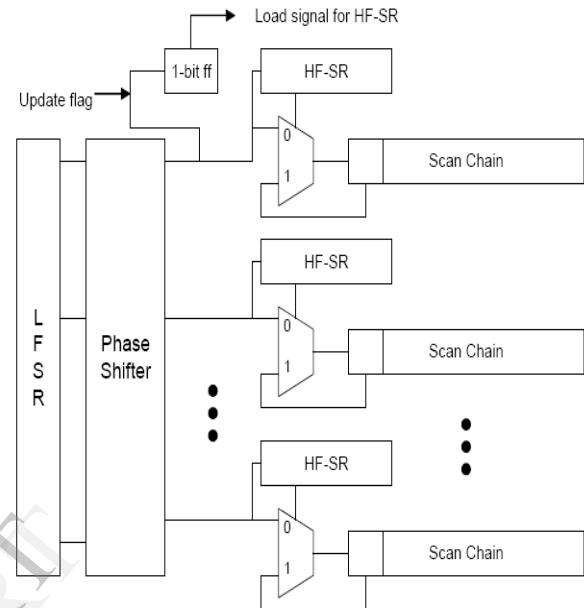

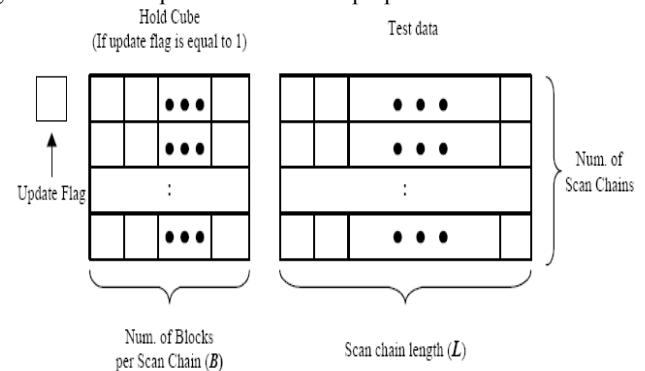

The hardware implementation for the proposed scheme is shown in Fig. 2. Each scan chain is divided into one or more blocks. Let  $B$  be the number of blocks per scan chain. Each scan chain has a hold flag shift register (HF-SR) whose size is equal to  $B$ . LFSR reseeding is used to generate all of the data for each test cube which consists of three components: update flag, hold flags, and test data. The format for the data coming out of the LFSR for each test cube is shown in Fig.3.

Fig 2. Hardware implementation of the proposed scheme

Fig.3 Data coming out of the LFSR for each test cube

The hardware implementation for the proposed scheme is shown in Fig. 3. Each scan chain is divided into one or more blocks. Let  $B$  be the number of blocks per scan chain [12]. Each scan chain has a hold flag shift register (HF-SR) whose size is equal to  $B$ . LFSR reseeding is used to generate all of the data for each test cube which consists of three components: update flag, hold flags, and test data. The format for the data coming out of the LFSR for each test cube is shown in Fig.3

## 4. HARDWARE IMPLEMENTATION

R.Karthick, Dr.V.Saminadan

There is a small finite state machine (FSM) controller that controls where the data coming out from the LFSR is loaded. In the initial clock cycle, the LFSR oscillates a single bit which is the update flag. If the revise flag is 1, after that B clock cycles, the LFSR oscillates the hold flags for each of the scan chains which are shifted into the HF-SRs. If the update flag is 0, then the HF-SRs are not loaded. Let the length of each scan chain be L.

Then for the next L clock cycles, the LFSR generates the test data. For each L/B clock cycles, if the corresponding hold flag for a scan chain is 0, after that the scan chain is stored from the LFSR. If the corresponding hold flag is a 1, after that the final value shifted into the scan chain is repeatedly shifted into the scan chain and the data from the LFSR is ignored. After each L/B clock cycles, the hold flag shift register is shifted so that the next hold flag becomes active for its corresponding block and is used as the control signal to a MUX (as shown in Fig. 2). After the scan chains have been filled, then the scan vector is applied to the circuit-under-test and the response is loaded back into the scan chain. The above mentioned process repeated to generate the next scan vector.

The hardware overhead consists of one 2-to-1 MUX and a HF-SR per scan chain, one 1-bit update flag flip-flop and the small FSM controller [10]. The FSM controller consists of a bit counter which is present for LFSR reseeding logic. The size of the HF-SR predominantly used to find the hardware overhead in reseeding scheme. It depends on the number of scan chains and the total number of blocks.

## 5. SIMULATION RESULTS

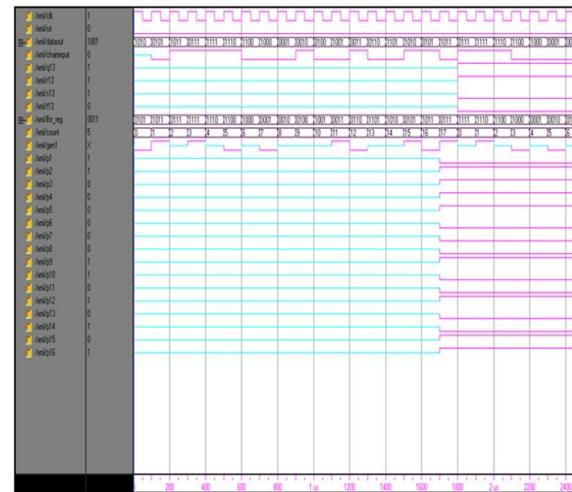

The code for LFSR and LFSR Reseeding with and without Encoding Algorithm code is written in VHDL and simulated using MODELSIM 5.7G

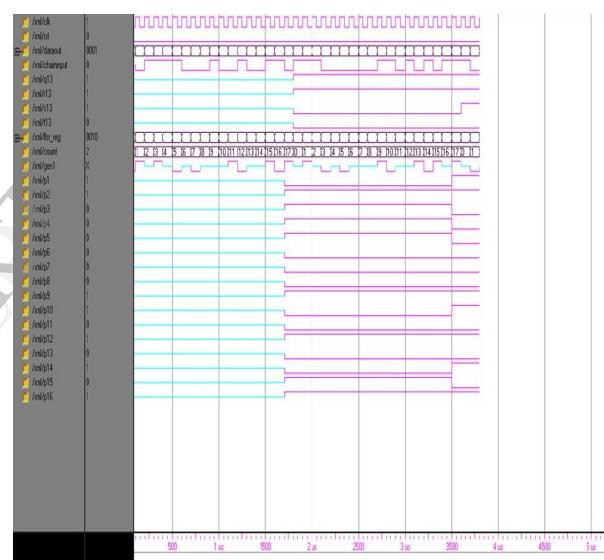

### 5.1 LFSR Reseeding Without Algorithm

By observing the result when the clock is high the LFSR generates the Test patterns and it shifted to the scan chain, the scan chain data are fed to input of the test circuit .In this method the test patterns are high, they take more time to process the data and it's power consumption is measured with the help of XILINX power analysis tool.

Fig 4 LFSR Reseeding without Algorithm (s27)

Fig 5 LFSR Reseeding without Algorithm (c17)

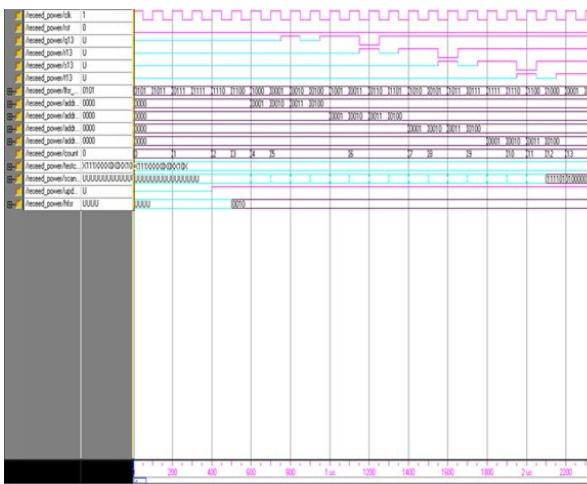

### 5.2 LFSR Reseeding With Algorithm

By observing the result when the clock is high the LFSR generates the Test patterns, if the hold flag is set, the encoded data are fed to the scan chain otherwise generated LFSR test patterns are fed to the scan chain. The scan chain data are fed to input of the test circuit, and its power consumption is measured with the help of XILINX power analysis tool.

R.Karthick, Dr.V.Saminadan

Fig 6. LFSR Reseeding With Algorithm

| Criteria         | Circuit name | LFSR reseeding without algorithm | LFSR reseeding with algorithm |

|------------------|--------------|----------------------------------|-------------------------------|

| Power in mw      | S27          | 21                               | 10                            |

| Power in mw      | C17          | 31                               | 15                            |

| Test data volume | S27          | 543                              | 256                           |

| Test data volume | C17          | 634                              | 342                           |

Fig 7. LFSR Reseeding With Algorithm

### Comparison of LFSR reseeding without algorithm along with LFSR reseeding with algorithm

The Method LFSR Reseeding without algorithm consumes more power and the device utilization is more, compare to LFSR Reseeding with circuit

## 6. CONCLUSION

LFSR reseeding is a powerful approach for reducing test storage. In this encoding scheme provides a technique to reduce test power for LFSR reseeding. It acts as a second stage of compression after LFSR reseeding. By employing hold flags, not only is test power reduced, but also test storage can be reduced. Further the Encoding scheme will be implemented in BIST Environment and will be tested with the help of Benchmark Circuits using MODELSIM and XILINX tools.

## REFERENCES

- [1] Chandra, A., and K. Chakrabarty (2001), "Combining low-power scan testing and test data compression for system-on-a-chip," Proc. of Design AutomationConf., pp. 166-169.

- [2] Chandra, A., and K. Chakrabarty( 2002), "Reduction of SOC Test Data Volume, Scan Power and Testing Time Using Alternating Run-length Codes," Proc. Of Design Automation Conference, pp. 673-678.

- [3] Rosinger, P. M., B.M. Al-Hashimi, and N. Nicolici(2002), "Low Power Mixed- Mode BIST Based on Mask Pattern Generation Using Dual LFSR Re-seeding," Proc. of Int. Conference on Computer Design, pp. 474-47.

- [4] Samaranayake, S., N. Sitchinava, R. Kapur, M.B. Amin(2002), and T.W. Williams, "Dynamic Scan: Driving Down the Cost of Test," Computer, Vol. 35, Issue 10, pp. 63 - 68.

- [5] Sankaralingam, R., R.R. Oruganti, and N.A. Touba(2000), "StaticCompaction techniques to control scan vector power dissipation," Proc. of VLSI Test Symp., pp. 35-40

- [6] N. Zacharia, J. Rajski, and J. Tyszer(1995), "Decompression of test data using variable-length seed LFSRs," in Proc. VLSI Test Symp., pp. 426-433.

- [7] Hellebrand, S., S. Tarnick, J. Rajski, and B. Courtois(1992), "Generation of Vector Patterns through Reseeding of Multiple-Polynomial Linear Feedback Shift Register," Proc. of International Test Conference, pp. 120-129.

- [8] Krishna, C.V., A. Jas, and N.A. Touba(2001), "Test Vector Encoding Using Partial LFSR Reseeding", Proc. of IEEE International Test Conference, pp. 885-893.

- [9] Hellebrand, S., J. Rajski, S. Tarnick, S. Venkataraman, and B. Courtois(1995),"Built-in Test for Circuits with Scan Based on Reseeding of Multiple-Polynomial Linear Feedback Shift Registers," IEEE Trans. on Computers, Vol. 44, No. 2, pp. 223-233.

R.Karthick, Dr.V.Saminadan

- [10] Krishna, C.V., and N.A. Touba(2001), "Reducing Test Data Volume Using LFSR Reseeding with Seed Compression ", Proc. of IEEE International Test Conference, pp. 321-330.

- [11] Koenemann, B(1991)., "LFSR-Coded Test Patterns for Scan Designs," Proc. of European Test Conference, pp. 237-242.

- [12] Jinkyu Lee and Nur A. Touba(2007),LFSR-Reseeding Scheme Achieving Low-Power Dissipation During Test", Proc. of European Test Conference, pp. 237-242.

IJERT

R.Karthick, Dr.V.Saminadan