# Survey of Electronic Hardware Testing Types, ATE Evolution & Case Studies

Manjula C Assistant Professor, EEE Dept., The Oxford College of Engineering, Bangalore

*Abstract* - I have undertaken exhaustive survey, to bring out this technical paper covering - Testing principle, Levels, Types, Process, VLSI or Chip testing, Automatic Test equipment (ATE) – configuration, evolution, three case studies of FPGA interfaced with ATE, FPGA generating ATG for ATE and FPGA used with PC scope for VLSI / Chip testing etc.

Keywords- Types of testing, Principle of testing, Levels of testing, ATE, Evolution of ATE Testing.

# INTRODUCTION

Testing is an experiment in which the system is exercised and its resulting response is analyzed to check its behavior [1]. If incorrect behavior is detected, the system is diagnosed and locates the cause of the misbehavior. Diagnosis requires the knowledge of the internal structure of the system under test.

## A. Importance of Testing

In Today's Electronics world, more time is required for testing rather than design and fabrication. When the circuit/device is developed, it is necessary to determine the functional and timing specifications of the circuit/device. When the multiple copies of a circuit are manufactured, it is essential to test each copy to verify whether the manufacturing process has introduced any flaws. In order to meet the requirements of the consumer, it is essential to test the circuit effectively, before it is released into the market.

Good Testing leads to:

- Better quality products

- Good brand value for company

- Total Customer satisfaction improves yield in manufacturing

# **B.** Testing Principle

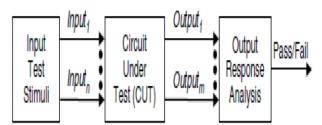

During Testing, a set of test stimulus are applied to the inputs of the Circuit/Device under test (CUT/DUT) and the output responses are analyzed [2], as illustrated in Figure1. Circuits that produce the correct output responses for all input stimuli are considered as fault-free and the circuits that fail to produce a correct response are assumed to be faulty.

# Fig.1: Basic Testing Approach

# C. Level of Testing

Testing a die (chip) can occur at the following levels:

- Wafer level

- Packaged chip level

- Board level

- System level

- Field level

# D. Types of Testing

Manual testing and Automated Testing:

Devices can be tested in two ways, manually and automatically. Testing Devices with human intervention is referred as Manual test. Testing devices with the help of programs or tools with minimal human intervention is referred as Automation test. Before Automation testing of any device, one must know how to test the particular device manually.

# E. Types of CHIP or VLSI TESTING

Advances in Fabrication technology have enabled VLSI engineers to use sub-micron technology which include millions of transistors in a single chip. As the number of transistors within the chip increases exponentially it results in smaller interconnection, shorting of drain and source of MOS [4] which results in the post manufacturing defects/faults in the chip, so post manufacture testing of VLSI Circuits is an important issue.

Tests fall into three categories. The First set of tests verifies whether the chip performs its intended function. This test is called functionality test or logic verification, verifies the functionality of the circuit [5]. The Second set of tests is run on the batch of chips that return from fabrication. These tests confirm whether the chip operates as intended and debug any discrepancies. They are more extensive than the logic verification tests because the chip can be tested at full speed in a system. For example, a new microprocessor can be placed in a prototype motherboard to try to boot the operating system. This silicon debug requires creative detective work to locate the cause of failures because the designer has much less visibility into the fabricated chip compared to during design verification [5].

The Third set of tests verifies whether the transistor, gate, and storage elements in the chip functions correctly. These tests are conducted on the chips before shipping to the customer. These are called manufacturing tests. In some cases, the same tests is used for all three steps, but it is better to use one set of tests for logic bugs and another set optimized to catch manufacturing defects. Testing methods are classified based on many criteria. Table 1 summarizes the important attributes of testing method and the associated terminology [5].

# F. Other Types of Testing

*Unit Test:* The first test in the development process is the unit test. The source code is divided into modules, which is further divided into smaller units called units [5]. These units have specific behavior. The test carried on these units of code is called unit test.

*System test:* Tests a device in its operating environment to ensure that it works properly when interconnected with other components. System testing is a kind of black box testing, which does not require the knowledge of inner design of system.

Fig.2: Various Electronics Automation Test Equipment's

*In-circuit test:* In-circuit test is a test that confirms that there are no shorts, resistances or other problems in the printed circuit boards (PCBs). It ensures proper manufacturing and quality of PCBs.

Ad Hoc Testing: Ad hoc test aims at reducing the combinational explosion of testing. This test is useful for small designs where scan, ATPG and BIST are not available.

*Parametric test:* It involves the testing of technologydependent parameters, such as power consumption, temperature etc.

*Operation and maintenance test:* Tests a product in the field for diagnosis or "preventive" purpose.

*Performance Testing:* Testing with the intent of determining how quickly a product handles a variety of events.

*Stress Testing*: Testing with the intention of determining how the product performs when a load is placed on the system resource that exceeds capacity.

Acceptance Testing: Testing the system with the intent of confirming readiness of the product and customer acceptance.

| Table 1: Types of testing                 |                                          |                                                |

|-------------------------------------------|------------------------------------------|------------------------------------------------|

| Criterion                                 | Attribute of Testing method              | Terminology                                    |

| When is testing performed?                | Concurrently with the normal system      | On-line testing                                |

|                                           | operation                                | Concurrent testing                             |

|                                           | As a separate activity                   | Off-line testing                               |

| Where is the Source of Stimuli?           | Within System itself                     | Self-testing                                   |

|                                           | Applied by an external device(tester)    | External testing                               |

| What do we test for?                      | Design Errors                            | Design Verification testing Acceptance testing |

|                                           | Fabrication errors                       | Burn-in                                        |

|                                           | Fabrication defects                      | Quality assurance testing                      |

|                                           | Infancy Physical failures                | Field testing                                  |

|                                           | Physical failures                        | Maintenance testing                            |

| What is the Physical Object being tested? | IC                                       | Component-level testing                        |

|                                           | Board                                    | Board-level testing                            |

|                                           | System                                   | System-level testing                           |

| How are the Stimuli and/or the expected   | Retrieved from storage                   | Stored-pattern testing Algorithmic testing     |

| response produced?                        | Generated during testing                 | Comparison testing                             |

| How are the stimuli applied?              | In a fixed(predetermined) order          |                                                |

|                                           | Depending on the results obtained so far | Adaptive testing                               |

| How fast are the stimuli applied?         | Much slower than the normal operation    | DC(static) testing                             |

|                                           | speed                                    | AC testing                                     |

|                                           | At the normal operation speed            | At-speed testing                               |

| What are the observed results?            | The entire output patterns               | Compact testing                                |

|                                           | Some function of the output patterns     |                                                |

| What lines are accessible for testing?    |                                          | Edge-pin testing                               |

|                                           |                                          | Guided-probe testing                           |

|                                           | Only the I/O lines                       | Bed-of-nails testing                           |

|                                           | I/O and internal lines                   | Electron-beam testing In-circuit testing In-   |

|                                           |                                          | circuit emulation                              |

| Who checks the Results?                   | The system itself                        | Self-testing                                   |

|                                           | An external device(tester)               | Self-checking                                  |

|                                           |                                          | External testing                               |

# II. AUTOMATED TEST EQUIPMENT

Automatic Test Equipment (ATE) plays a vital part of the electronics test. The success of tablets, PDAs has created a demand for greater functionality in terms of speed, performance and pin counts of products which has led to an increasing demand of ATE.

Automated test equipment is a computer controlled test and measurement equipment to test the logic units with minimal human intervention. An ATE can be a simple computer controlled digital multimeter or a complicated system having dozens of complex test instruments which is capable of testing automatically and diagnosing faults in System-On- Chips or Integrated circuits to ensure that the end product functions correctly.

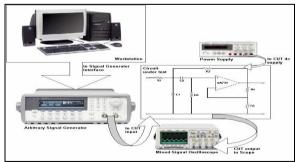

Fig.3 Broad view of Automatic Test Equipment

The advantages of the ATE are, they are repeatable and cost efficient in high volume Testing or in Product test environment. The disadvantages of ATE are upfront costs, programming and setup [6]. ATE is expensive and therefore it is necessary to ensure that the correct test philosophy and the correct type of automatic test equipments are used.

# A. General Configuration of the ATE

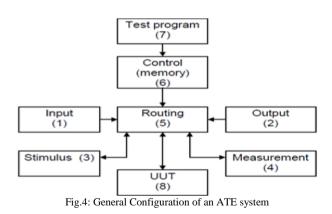

The general configuration of an ATE system is shown in Figure 4. It is generally applicable from the earliest configuration of ATE to current systems.

*Input* – the ATE input subsystem allows the ATE operator to select the operating mode under which the system will perform and provides the various media by which the operator can communicate with the system, i.e. tape, Compact Disk (CD), keyboard, floppy.

*Output* – the output subsystem provides the means by which the ATE system communicates with the ATE operator. This can include visual indicators (lights), cathode ray tubes, printers and even voice.

*Stimulus* – the stimulus subsystem consists of programmable devices which provide either power or signals to UUT. The functional capability of devices is controlled by the input stimulus without human intervention.

*Measurement* – the measurement subsystem consists of programmable devices which can assess the parametric values of power or signals from a UUT.

*Routing* – the routing subsystem consists of switching devices by which program control is capable of interconnecting the outputs or the inputs to designated locations on a UUT.

*Control* – the control subsystem manages the operation of the ATE, it takes the signals from the input subsystem and controls the system operation based on these inputs. The control system interprets the test instructions and selects the appropriate stimulus device and establishes the routing configuration to connect the stimulus.

*Test program* – the test program is a set of coded instructions which determines the tests to be performed and the consequence of passing or failing the test.

UUT – The Unit under test is the device that is assessed by the ATE in conjunction with the test program.

# B. Evolution of ATE systems

# First Generation

The First Generation ATE was introduced between 1955 and 1965. They are characterized by single function stimulus devices programmed by the ATE manufacturers. These systems are controlled by specially designed digital devices. The component technology used in this system consists of discrete components and vacuum tubes. These systems were quite large, used a great deal of power and were designed for test of a single, specific UUT.

# Second Generation

The Second Generation ATE was founded between 1962 and 1972. These ATE systems are characterized by the use of general purpose bench top instruments for Stimulus and measurement. Control of the second generation ATE is accomplished by a general purpose computer having the characteristics of today's desktop computers although they are larger and limited in performance, speed and memory size.

# Third Generation ATE

Third generation ATE was introduced between 1970 and 1980 which uses computer systems and sophisticated software which replaces the stimulus and measurement building blocks used in second generation ATE. This ATE has unique attributes: they utilize DACs for signals synthesizing; the signal characteristics are predicated based on the mathematical definition of the signal. The benefits of these ATEs are small size and broad flexibility.

# Fourth generation ATE

The fourth generation of ATE began in the late 1980s. The significant changes are made in fourth generation ATE which includes increasing sophistication of the computer systems, enormous increase in memory availability and the extensive use of distributed micro-processing, hybrid arrays and other technological innovations.

# Current ATE

The current ATEs are driven by the significant expansion of processing capability and by recognition of instrument manufacturers [9]. Software systems within ATE are capable of archive data; provide guidance and instruction to operators and assists in management and queuing of UUTs.

# C. Types of Automated Test Equipment's

The most widely used automatic test equipment is listed below [5]:

# PCB inspection systems:

PCB inspection is a key element in any production process, particularly used where pick and place machines is involved. Initially manual inspection was used, which was unreliable and inconsistent. Now PCBs are more complicated and manual inspection is not a viable option. Accordingly automated systems are used:

# Automatic Optical Inspection (AOI):

The AOI systems are generally located after the PCB solder process. AOI machine consists of multiple, high resolution cameras, situated at different angles, which captures images from all parts of the board and enables inspection of complex boards in a short time with high levels of accuracy [8]. It locates production problems including solder defects, checks whether the proper components are fitted and also the orientation of the components.

# Automated X-Ray inspection (AXI):

Automated X-Ray inspection is similar to AOI. The X-Ray inspection equipment captures a high resolution X-Ray image that allows inspection of devices. AXI systems can examine the solder joints underneath the package to evaluate the solder joints.

# In circuit test (ICT):

In-Circuit Test is particularly an effective form of PCB test. This test technique examines the short circuits, open circuits, component values and also checks the operation of ICs.

# Manufacturing Defect Analyzer (MDA):

MDA is another form of PCB test and is a simplified form of ICT. This form of PCB test, tests the manufacturing defects, short circuits, open circuits and component values. Cost of these test systems is much lower than that of a ICT, but the fault coverage is less.

## JTAG Boundary scan testing:

It is known as JTAG (Joint Test Action Group) with standard IEEE 1149.1. It offers significant advantages over other traditional forms of testing [7]. Because of its ability to test boards and ICs with limited physical test access, Boundary Scan / JTAG is widely used.

## Functional testing:

Functional test is a form of electronics testing that exercises the functionality of a circuit [6]. There are number of approaches that can be adopted based on the type of circuit (RF, digital, analogue, etc). The main approaches are outlined below:

## Functional Automatic Test Equipment (FATE):

These ATE systems are generally used for testing digital boards. The increasing speeds at which boards run these days cannot be accommodated on these testers and fixtures are expensive. Despite of these drawbacks, these testers is still used in areas where production volumes and speeds is not high.

## Rack and stack test equipment using GPIB:

Boards or units can be tested themselves by using a stack of remotely controlled test equipment. The General Purpose Interface Bus GPIB initially known as Hewlett Packard Interface Bus (HPIB) and is also referred as the IEEE 488 bus. It was developed as a means of controlling test equipment for ATE systems.

## Chassis or rack based test equipment:

synchronously by an external computer.

The idea of test instruments within a chassis was developed by the VXI (VME extensions for Instrumentation) guise. The system uses test instruments on a card that can be slotted into a standard chassis. This saves both space and cost when compared to the stand-alone instruments and also increases the communication speed.

#### **III. CASE STUDIES**

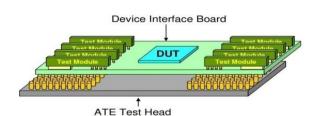

Case Study 1 – FPGA interfacing with ATE The Device Interface Board (DIB) is designed to accommodate test enhancement modules. Figure 5 shows a conceptual cutaway view of an ATE test head, with a multi-layer PCB DIB. Multiple test modules connect the top side of the DIB and are controlled

Fig.5: ATE test head shown with device interface board [1].

XOR Ch1 Logic Ch2 Logic FPGA 4 Prog Delays Flash USB

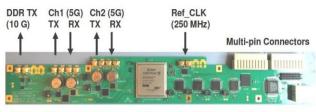

#### Fig.6: photograph of the test module [1]

In most production testing environments where robotic handlers are used, the test modules are connected to the bottom side of the DIB. Low speed data and control signals connect between the test module and ATE, while highperformance test signals connect between the module and DUT.

Figure 6 shows a photograph of the test module. In this figure the core logic consists of FPGA, USB microcontroller, flash, etc. is located in the central and right side of the board, along with four programmable delay chips (for the reference clocks) and the multi-pin Gbps signal connectors.

Application-specific logic is located on the left side of the board, including the SiGe select logic, adjustable-amplitude buffers; fan out buffers, relays and SMP connectors.

## Case Study 2 – FPGA generates ATG for ATE

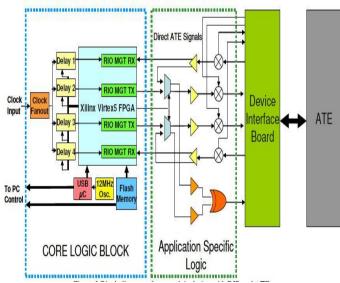

The Test Module is designed in two blocks as shown in Figure 7. The first block is a core component that exploits state-of-the-art field programmable gate array (FPGA) technologies. The use of an FPGA allows the test system to operate independently of the ATE [12].

Fig.7: Block diagram of test module design with DIB and ATE

With the FPGA, the core component controls and generates many test functions itself [10]. However, in most test applications, simple DC tests such as I/O voltage and current measurement are also required and are better handled by existing ATE resources. To retain full testing functionality, the designed solutions must be compatible with existing ATE infrastructure.

Therefore the test module is designed with provisions to allow direct access to ATE signals, thus retaining full ATE functionality.

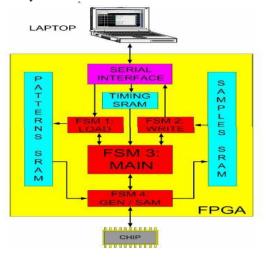

Fig.8: Block scheme of architecture on FPGA used to interface laptop with chip under test

## Case Study 3 - Automatic Test Pattern Generation (ATPG)

Test Generation (TG) is the process of determining the stimuli to test a digital system. TG depends on the testing method employed. On-line testing methods do not require TG. Automatic test generation (ATG) refers to TG algorithms that, given model of a system can generate tests for it [11].

Historically, in the IC industry, logic and circuit designers implemented the functions at the RTL or schematic level, mask designers design the layout and test engineers write the tests. For the longest time, test engineers implored circuit designers to include extra circuitry to ease the burden of test generation. As processes have increased in density and chips have increased in complexity, the inclusion of test circuitry has become less of an overhead for both the designer and the manager worried about the cost of the die. In addition, as tools have improved, more of the burden is for generating.

A test has fallen on the designer. To deal with this burden, Automatic Test Pattern Generation (ATPG) methods have been invented. The use of some form of ATPG is standard for most digital designs.

# CONCLUSION

Automated Test Equipment (ATEs), available in the market is very expensive. My Research mainly focused on developing a low cost "FPGA based Scalable Universal Digital ATE" that is used to test all kinds of Combinational Circuits, Sequential Circuits, Processors, Memories, SOC, PCB etc.

#### REFERENCES

- [1] MironAbramovici, Melvin A. Breuer, Arthur D "Digital Systems Testing and Testable Design" The institute of Electrical and Electronics Engineers, Inc, New York.

- [2] S. Asvini, C.Nirmala "Design for Testability in Timely Testing of Vlsi Circuits" Int. Journal of Engineering Research and Applications www.ijera.com ISSN : 2248-9622, Vol. 5, Issue 3, (Part -2) March 2015.

- [3] https://smartbear.com/learn/automated-testing/what-is-automated-testing/

- [4] https://en.wikipedia.org/wiki/Automatic\_test\_pattern\_generation

- [5] "Modern ASIC Design" by Dian Zhou.

- [6] Automatic test equipment ATE Primer

- [7] https://en.wikipedia.org/wiki/Functional\_testing\_(manufacturing)

- [8] JTAG/Boundary Scan Design for Testability.

- [9] Automatic optical inspections-electronic notes.

- [10] Keezer D C "Multi-Function Multi-GHz ATE Extension using Stateof-The-Art", Test conference (ITC) 2011 IEEE.

- [11] http://eecs.ceas.uc.edu/~wjone/Comb-TG.pdf

- [12] Hao Chen, Yu Chen, Douglas H, "A Survey on the Application of FPGAs for Network Infrastructure Security" Summerville IEEE COMMUNICATIONS SURVEYS & TUTORIALS, 2010.