# Steady State And Dynamic Behavior Of DC/AC Ideal Half Bridge Two Level Voltage Source Converter

Prof. P. Swaminathan, Assistant Professor [SG]/EEE, Karunya School of Electrical Sciences, KARUNYA University, Coimbatore – 641114

#### Abstract

This paper presents steady state and dynamic performance of a single phase DC/AC ideal half-bridge two-level inverter. The principle of operation of this inverter is described and the main theoretical waveforms are presented, as well as the simulation results. The main expressions for the design of the inverter are also presented. This inverter presents the following advantages of lossless inverter; the THD at the load is also preferably very less. The load current is divided amongst the switches, therefore reducing the conduction losses. In light of its characteristics, we believe that it is appropriate for industrial applications.

# **1. Introduction**

Power semiconductor switches are the main building blocks of power electronic converters. The trend in the development of power semiconductor switches [1, 2] points toward ever increasing utilization of electronic switches. The effort to increase the maximum permissible switching frequency and to minimize switching and conduction losses is the subject of major research and development programs of the power semiconductor switch industry. The characteristics of a power electronic converter mainly depend on the type of its semiconductor switches. It is therefore warranted to briefly review different switch types. Further details regarding the operation and characteristics of the most commonly used switches can be found in Refs. [3, 4]. In power conversion, semiconductor switches are almost exclusively used in the switching mode, that is, the switch is either in the on state or in the off state. The steady-state and switching properties of an electronic switch are conventionally illustrated and characterized by, respectively, the switch current/voltage waveforms and the characteristic curves in the current versus voltage (v-i) plane. For system studies and control design purposes, especially for high-power converters where the switching frequencies are typically low, simplified switch models are often adopted. Such models retain the device features relevant to the study, while considerably reduce the

modeling, analytical, and computational burden. However, depending on the objectives of a specific investigation, the accuracy of waveforms and results can be enhanced if more elaborate switch models are employed. For example, if the switching loss of a converter is of interest, the diode reverse recovery and the transistor tailing current effects [3] must be included in the model of switches.

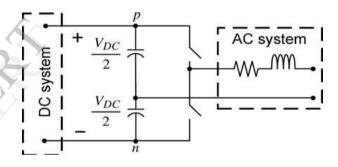

# 3. Basic Half Bridge VSC

Fig.1.1 Basic Half Bridge VSC

Figure 1.1 shows the basic circuit diagram of a halfbridge, single-phase, two-level VSC. The half-bridge VSC consists of an upper switch cell and a lower switch cell. Each switch cell is composed of a fully controllable, unidirectional switch in antiparallel connection with a diode. This switch configuration constitutes a reverse-conducting switch that is readily available, for example, in the form of commercial IGBT and IGCT. The DC system that maintains the net voltage of the split capacitor can be a DC source, a battery unit, or a more elaborate configuration such as the DC side of an AC/DC converter. The half-bridge VSC of Figure 3.1 is called a two-level converter since the switched AC-side voltage, at any instant, is either at the voltage of node p or at the voltage of node n, depending on which switch cell is on. The fundamental component of the AC-side voltage is usually controlled based on a pulse-width modulation (PWM) technique [3, 7].

### 4. Converter Model

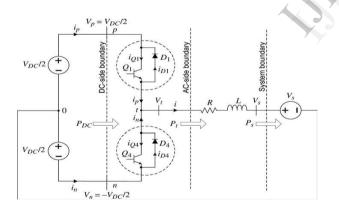

Figure 2.1 shows a schematic diagram of a DC/AC half-bridge converter . The half-bridge converter is composed of two switch cells. The upper and lower switch cells are numbered 1 and 4, respectively. Each switch cell is realized by antiparallel connection of a fully controllable unidirectional switch and a diode. Thus, the upper switch cell consists of the transistor Q1 and the diode D1. Similarly, the lower switch cell is composed of the transistorQ4 and the diodeD4. As Figure 2.1 shows, in each transistor the positive current is defined as the current flowing from the collector to the emitter. The positive current in the diode is defined as the current flowing from the anode to the cathode. The currents through the upper and lower switch cells are denoted by ip and in, respectively, as shown in Figure 2.1. Thus, ip = iQ1 - iD1 and in = -(iQ4 - iD4). Nodes p and n in Figure 2.1 signify the DC-side terminals (or the DC side) of the half-bridge converter. Similarly, we specify the AC-side terminal (or the AC side) of the half-bridge converter by node t. From the DC side, the half-bridge converter of Figure 4.1 is connected to two identical DC voltage sources, each with a voltage of VDC/2. The common point of the voltage sources is labeled as node 0. We refer to this node as the DC-side midpoint and choose it as the voltage reference node.

Fig.2.1 Power Circuit Diagram of Half Bridge Two Level VSC

From the AC side, the half-bridge converter is interfaced with the voltage source Vs, which we refer to as the AC-side voltage source. The negative terminal of the AC-side voltage source is connected to the DCside midpoint. The connection between the AC-side terminal and the AC-side voltage source is established through an interface reactor represented by a series RL branch. The AC-side terminal voltage, Vt, is a switched waveform and contains voltage ripple. Thus, the interface reactor acts as a filter and ensures a low-ripple AC-side current. L and R, respectively, represent the inductance and the internal resistance of the interface reactor. In some cases, the load or the AC-side source embeds the interface reactor, and no external RL branch is provided. For example, in an electric drive system, the inductance of the machine stator is utilized as the interface reactor between the converter and the machine. In Figure 2.1, *PDC* represents the (instantaneous) power at the DC side, *Pt* denotes the power at the AC side, and *Ps* signifies the power delivered to the AC-side voltage source. The positive direction of the power flow is defined from the DC voltage source(s) toward the AC-side voltage source.

#### 5. Principle of Operation

The half-bridge converter operates based on the alternate switching of Q1 and Q4. The turn-on/off commands of Q1 and Q4 are issued through a pulse-width modulation (PWM) strategy. The intersections of the carrier and the modulating signals determine the switching instants of Q1 and Q4. Once the modulating signal is smaller than the carrier signal, the turn-on command for Q1 is blocked while a turn-on command is issued for Q4. It should be noted that a switch does not necessarily conduct if it is commanded to turn on; the switch conducts only if the turn-on command is provided and the current direction conforms to the switch characteristics. For example, in response to a turn-on command, an IGBT can conduct only if the current flow is from the collector to the emitter.

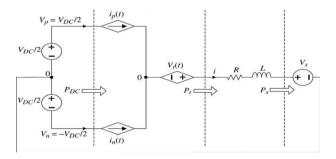

Fig.3.1 Dynamic Model of the half-bridge converter

To employ the half-bridge converter as a component of a larger system, we need to identify the characteristics of the converter as observed from its terminals. The switched model of the half-bridge converter introduces the relationships among the converter terminal voltages and currents. A comparison between Figures 2.4 and 2.5 indicates that in a switch cell the waveform of the current through the transistor, or that through the diode, depends on the direction of the converter AC-side current. Since ip = iQ1 - iD1 and in = -iQ4 + iD4, the waveform of the switch cell current is independent of the polarity of *i*. More importantly, the waveform of the AC side terminal voltage Vt is independent of the polarity of *i* and is uniquely determined by the switching functions. When s1 = 1, the upper switch cell is closed and the lower one is open; therefore, Vt = Vp = VDC/2, ip = i, and in = 0. Alternatively, when s4 = 1, the lower switch cell is closed but the upper one is open; consequently, Vt = Vn = -VDC/2, ip = 0, and in = i. This holds for both i > 0 and i < 0, as illustrated in Figure 2.6. It follows from the foregoing discussion that the half-bridge converter of Figure 2.1 can be mathematically characterized by

$$s_{1}(t) + s_{4}(t) \equiv 1,$$

$$S_{1}(t) = (V_{DC}/2)s_{1}(t) - (V_{DC}/2)s_{4}(t) = 0.$$

$$S_{1}(t) = (V_{DC}/2)s_{1}(t) - (V_{DC}/2)s_{4}(t) = 0.$$

$$(100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100) = (100$$

$$i_{p}(t) = is_{1}(t),$$

$i_{n}(t) = is_{4}(t).$

6.3

6.4

Equations (6.1)–(6.4) describe the relationships between the half-bridge converter terminal voltages/currents and the switching functions. Figure 3.1 illustrates a switched equivalent circuit for the halfbridge converter of Figure 2.1, based on (6.1)–(6.4).

PDC, Pt, and Ps are calculated as

$$P_{DC}(t) = V_p i_p + V_n i_n = \frac{V_{DC}}{2} [s_1(t) - s_4(t)] i,$$

$$P_t(t) = V_t(t) i = \frac{V_{DC}}{2} [s_1(t) - s_4(t)] i,$$

6.6

$$P_s(t) = V_s i. 6.7$$

$$P_{loss} = P_{DC} - P_t. ag{6.8}$$

# 7. Steady State and Dynamic Analysis

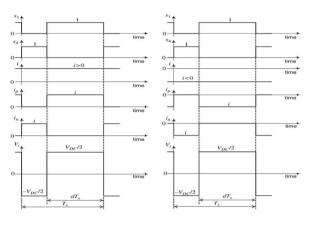

#### 7.1 Positive AC-Side

The half bridge converter of Figure 2.1 with a positive AC-side current *i*. Assume that s1 = 0 and thus Q1 is blocked. Consequently, *i* cannot flow through D1, since *iD*1 cannot be negative. For the same reason, Q4 does not carry *i*, although s4 = 1. Therefore, *i* flows through D4 and Vt = Vn = -VDC/2. Now consider a time instant

a. Positive AC Side b. Negative AC Side

at which s1 = 1 and s4 = 0. In this case, Q1 conducts while Q4 is blocked. When Q1 is on, we have Vt = Vp= VDC/2, and D4 is reverse biased. Therefore, *i* flows through Q1. The waveforms of the half-bridge converter for positive *i* are given below.

# 7.2 Negative AC-Side

It follows from a similar analysis as presented for the case of positive *i* that Q1 and D4 do not take part in the converter operation when *i* is negative. In this case, when s4 = 1, Q4 conducts and Vt = Vn = -VDC/2. Alternatively, when s4 = 0, the AC-side current passes through D1 and Vt = Vp = VDC/2. The duty ratio, *d*, is defined in the same way as in the case of the positive AC-side current. Figure illustrates the waveforms of the half-bridge converter for negative *i*.

# 7.3. Simulation Model

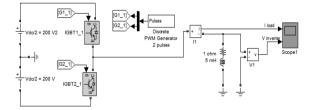

Fig.8.1 Simulation Model of Ideal Half-Bridge VSC

# 7.4. Simulation Results

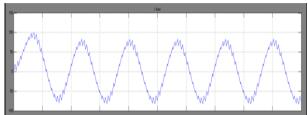

4.1. Positve and Negative AC side waveform

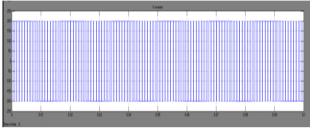

4.2. Voltage at Inverter Terminals

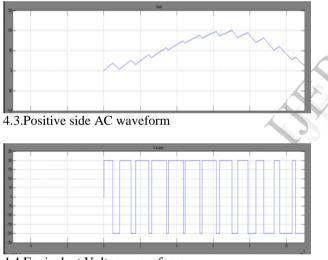

4.4.Equivalent Voltage waveform

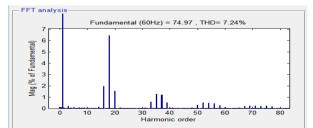

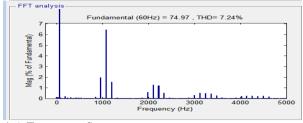

4.5. Harmonic order of selected signal

4.6. Frequency Spectrum

# 8. Conclusion

It is notify that the switched model equations that *Ploss*  $\equiv 0$ , that is, the ideal half-bridge converter is lossless. The switched model accurately describes the steadystate and dynamic behavior of the converter. The accuracy can be enhanced if more elaborate models are adopted for the circuit components, for example, switches. Thus, given the switching functions for the transistors, the instantaneous values of the current and voltage variables can be computed by means of the switched model. Therefore, the computed variables include high-frequency components, for example, due to the switching process, as well as slow transients.

# 9. Future work

The relationships between the modulating signal, which is the main control variable and the current, voltage variables are not easily understood from the switched model. Moreover, for dynamic analysis and control design purposes, knowledge about the high-frequency details of variables is often not necessary, as the compensators and filters in a closed-loop control system typically exhibit low-pass characteristics and do not react to high-frequency components. For these reasons, we are often interested in the dynamics of the average values of variables, rather than in the dynamics of the instantaneous values.

# References

1. K. Satoh and M. Yamamoto, "The Present State of the Art in High Power Semiconductor Devices," Proceedings of the IEEE, vol. 89, no. 6, pp. 813–821, July 2001.

2. B. J. Baliga, "The Future of Power Semiconductor Device Technology," Proceedings of the IEEE, vol. 89, no. 6, pp. 822–832, July 2001.

3. N. Mohan, T. M. Undeland, and W. P. Robbins, Power Electronics, Converters, Applications, and Design, 3rd edition, Wiley, 2003.

4. B. Wu, High-Power Converters and AC Drives, Wiley/IEEE, 2006.

5. A. Alesina and M. G. B.Venturini, "Analysis and Design of Optimum-Amplitude Nine-Switch Direct AC–AC Converters," IEEE Transactions on Power Electronics, vol. 4, no. 1, pp. 101–112, January 1989.

6. S. B. Dewan and A. Straughn, Power Semiconductor Circuits, Wiley, 1974.

7. D. G. Holmes and T. A. Lipo, Pulse Width Modulation for Power Converters:

Principles and Practice, Wiley/IEEE, 2003.

8. M. Saeedifard, H. Nikkhajoei, R. Iravani, and A. Bakhshai, "A Space Vector

Modulation Approach for a Multimodule HVDC Converter System," IEEE Transactions on Power Delivery, vol. 22, no. 3, pp. 1643–1654, July 2007.

9. M. Hagiwara, H. Fujita, and H. Akagi, "Performance of a Self-Commutated

BTB HVDC Link System Under a Single-Line-to-Ground Fault Condition," IEEE Transactions on Power Electronics, vol. 18, no. 1, pp. 278–285, January 2003.

10. C. Schauder, M. Gernhardt, E. Stacey, T. Lemak, L. Gyugyi, T.W. Cease, and

A. Edris, "Development of ±100 MVAR Static Condenser for Voltage Control

of Transmission Systems," IEEE Transactions on Power Delivery, vol. 10, no.

3, pp. 1486–1493, July 1995.

11. H. W. Van Der Broeck, H. Skudelny, and G. V. Stanke, "Analysis and Realization of a Pulsewidth Modulator Based on Voltage Space Vectors," IEEE Transactions on Industry Applications, vol. 24, no. 1, pp. 142–150, January/February 1988.

12. R. Wu, S. B. Dewan, and G. R. Slemon, "Analysis of an AC-to-DC Voltage

Source Converter Using PWM with Phase and Amplitude Control," IEEE Transactions on Industry Applications, vol. 27, pp. 355–364, March/April 1991.

13. A. Nabavi Niaki and M. R. Iravani, "Steady-State and Dynamic Models of Unified Power Flow Controller (UPFC) for Power System Studies," IEEE Transactions on Power Systems, vol. 11, pp. 1937– 1942, November 1996.

14. J. A. Sanders and F.Verhulst, Averaging Methods in Nonlinear Dynamic Systems, Springer-Verlag, 1985.

15. H. A. Khalil, Nonlinear Systems, 3rd edition, Prentice-Hall, 2002.

16. J. G. Kassakian, M. F. Schlecht, and G. C. Verghese, Principles of Power Electronics, Addison-Wesley, 1991.

17. P. T. Krein, J. Bentsman, R. M. Bass, and B. L. Lesieutre, "On the Use of

Averaging for the Analysis of Power Electronic Systems," IEEE Transactions

on Power Electronics, vol. 5, pp. 182–190, April 1990.

18. R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd

edition, Kluwer Academic Publishers, 2001.

19. K. Thorborg, Power Electronics, Prentice-Hall, 1988.

20. J. S. Lai and F. Z. Peng, "Multilevel Converters: A New Breed of Power Converters," IEEE Transactions on Industry Applications, vol. 32, pp. 509–517, May/June 1996.