#### **ICEI - 2022 Conference Proceedings**

# Seven Level Multilevel Inverter with Reduced Switches using Novel Design

Latif Unnisa

Department of Electrical & Electronics Engineering The Oxford College of Engineering Bommanahalli, Bengaluru, India Jayakumar N

Department of Electrical & Electronics Engineering

The Oxford College of Engineering

Bommanahalli, Bengaluru, India

Someswari T

Department of Electrical & Electronics Engineering

The Oxford college of Engineering

Bommanahalli, Bengaluru, India

Abstract— The Multilevel inverter usage has been expanded since the last 10 years. These new sorts of inverters are appropriate in different high power and high voltage applications because of their capacity to orchestrate waveforms with improved yield. This venture presents equipment seven level staggered inverter, utilizing microcontroller-based equipment. The staggered inverters certainly stand out enough to be noticed because of the particularity and effortlessness of control. The advancement of high-voltage semiconductors to drive inverter frameworks proceeds. According to a pragmatic perspective, staggered inverters can be founded on reasonable arrangements for applications where a high result voltage can be created utilizing medium voltage gadgets. Notwithstanding this central trademark, staggered inverters have top-notch execution because of the age of a ventured yield voltage nearer to the sine waveform which decreases the sounds in the result waveform.

Keywords— MLI-multi level inverter; Microcontroller; Octo coupler; Mosfet.

#### I. INTRODUCTION

Power gadgets circuits assume crucial part underway of power utilizing environmentally friendly power sources. It is principally used to change over and control the sign. It changes over the sources, possibly it from DC/AC to AC/DC. The AC sources switched over completely to DC source is called rectifier and the DC source changed over completely to AC source is called inverter. The inverter changes over electrical energy. Staggered inverters are applied in space of high-power and medium voltage applications. It delivers an ideal MLI yield voltage from the different DC sources. The staggered inverter focuses because of its benefits in lower exchanging misfortune better electromagnetic similarity, lower music and higher voltage ability. The underlying inverters created were exclusively of two levels. The innovation got progressed and staggered inverters were created which can deliver an ideal result of various voltage levels from many sources of info DC voltage sources.

Staggered Inverter is one of the potential arrangements which is material in numerous applications frameworks. They are able to use in high voltage application with low symphonious additionally and effectively give the require power levels required by the high voltage drives.

#### II. LITERATURE SURVEY

#### 1. Niraj VijayShankar Mishra (2020)

In this venture staggered inverter with switches. A Multilevel inverter is one sort of successful and pragmatic answer for the rising power interest and diminishing music of ac waveforms. This Multilevel inverter requires eight changes to accomplish the staggered yield. By diminishing switches and expanding levels will decrease channel costs, consonant substance, lessening exchanging misfortunes and expenses.

#### 2. Jyoti M. Kharade (2017)

In this paper, three level, five level and seven level flowed H-span inverters have been reproduced by utilizing MATLAB/SIMULINK. The aftereffects of reproduced arrangement of Multilevel Cascaded H-Bridge inverter have been looked at based on changed boundaries, for example, number of switches, number of DC sources expected for activity.

#### 3. Wahyu Mulyo Utomo, Afarulrazi (2018)

This paper presents a model of staggered inverter utilizing 7-level Cascaded H-Bridge of staggered DC-AC inverter to lessen complete symphonious contortion with various sinusoidal heartbeat width regulation like stage demeanor and stage resistance attitude. Recreation result of single-stage staggered inverter flowed H-span are investigated and confirmed in the MATLAB/Simulink programming. The outcome shows that the 7-level flowed H-Bridge staggered inverter with stage attitude procedure create less all out symphonious bending assuming it is contrasted with the stage resistance demeanor method.

## 4. C.S. Sharma, Rahul Tamrakar (2016)

This paper presents most recent improvement of demonstrating and control of a solitary stage 7 - level outpouring staggered DCAC network associated inverter. Every inverter span is related with a sunlight-based charger. The consequences of MATLAB demonstrating of the framework detail the similar investigation of inverter geographies which is the staggered inverter geography with diminished number of switches with almost sinusoidal result,

in this manner decreasing entryway driver circuit and format of upgrading circuit which lessens THD, misfortunes, exchanging pressure, EMI.

#### 5. Sze Sing Lee (2018)

Another MLI geology that requires just a singular DC source and is great for making seven voltage levels with triple voltage helping gain. Three H-ranges are interconnected through two bidirectional voltage impeding changes to draw in the split the difference of two exchanged capacitors.

#### 6. Mahammed Sameer m Attar (2016)

This paper proposes a single stage five level inverter for network related (PV) system. The outcome current of the inverter can be changed by the voltage of the photovoltaic (PV) display. This control scheme relies upon SPWM topography. Plans considering SPWM which needn't bother with the help of a phase locked circle for cooperating the inverter to the grid are dynamically being used for such applications. Execution evaluation of the five-level inverter is done on MATLAB stage. The reasonableness of the proposed plot is certified by performing reenactment and results endorsement.

#### 7. Abhishek Kumar Ranjan (2015)

The goal of this paper was to execute all the level-shift PWM philosophy to changed streamed H-range inverter. Their Fourier assessment of THD has been learned at various transporter frequencies and at various voltage levels. For this Five-level, Seven-level, Nine-level, 11-level, 13-level and 21-levels of voltage has been copied. Their taking a gander at FFT evaluation has accomplished for resistive weight.

### 8. Krishna Kumar Gupta, Lalit Kumar, Shailendra Jain (2012)

Another half-and-half inverter is proposed which uses six dynamic changes alongside hilter kilter source setup to blend 7-level waveform. A flowed H-span inverter with comparable source design would require eight dynamic switches, all working at high exchanging recurrence. A tweak methodology is proposed utilizing which the switches with most elevated obstructing voltages work at principal recurrence.

## 9. Shreya Bandil1, Sadbhawna Kushwaha2, Shivani Soni3, Yogita Rathode4 (2020),

Proposed MLI incorporates single source, less scope of switches, diodes and capacitors, all out consonant mutilation, and symphonious range. Consequently, proposed Cascaded Multilevel Inverter decreases the intricacy of circuit design.

#### 10. Ruhina R. Shaikh, Prof. J.R. Rana (2016)

The obligation to the inverter given is a DC source (Vdc) and is great for conveying result of 7 level (Vdc, 2Vdc/3, Vdc/3, 0, - Vdc, - Vdc/3, - Vdc/3). The exchanging gadgets utilized are diodes and IRF840 MOSFET. Little Regulator is utilized for Controlling circuit for finishing the H-length inverter. Design proposed in this is having lesser number of exchanging gadgets that lessens the intricacy of the circuit and an immediate control circuit is utilized the limited scale regulator.

#### 11. Ruhina R. Shaikh (2016)

Execution of the single stage 7 level inverter with PWM control plot. Commitment to the given inverter is dc source (Vdc) and it is truly perfect for making result of seven level (Vdc, 2Vdc/3, Vdc/3, 0, - Vdc, - Vdc/3, - Vdc/3). As extra means are summed up to waveform, symphonious twisting of the outcome waveform lessens. The trading contraptions used are 25N120 IGBT and diodes. Control circuit for doing the Hrange inverter is done by using the more unassuming than normal controller.

#### III. OBJECTIVE OF THE WORK

The principal objective of this task is executed inverter which a gadget or electric circuit that convert direct momentum to rotating ebb and flow is one of the electronic gadgets that give worry to analysts for development of creating a slick power source. The result will be 7 level stepwise.

#### IV. PROBLEM STATEMENT

The underlying inverters created were exclusively of two levels. The innovation got progressed, and staggered inverters were created which can deliver an ideal result of various voltage levels from many sources of info DC voltage sources. Multilevel Inverter is one of the potential arrangements which is pertinent in numerous applications frameworks. They are competent to use in high voltage application with low symphonies additionally and effectively give the requirement power levels required by the high voltage drives.

#### V. PROPOSED METHODOLGY

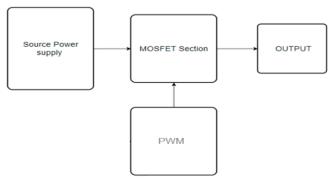

The diminished Multilevel inverter likewise makes 7 result levels like the standard H Bridge Multilevel inverter yet purposes 8 switches because of which we can diminish exchanging difficulties. The information voltage divider is made for section input in three branches. Resulting to going between the potential divider the separated voltage occurs after that given to this exchanging area in this way exists make utilizing MOSFETs, along with four diodes. This voltage is next dispatch through the H-development to this result terminal that incorporates four MOSFET. The MOSFET entry will procure influence from PWM block in age and in gear we are including microcontroller and Optocoupler locale for trigger MOSFET.

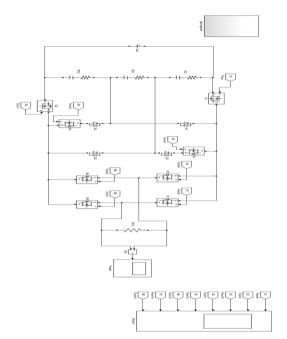

Fig (1) Simulation Diagram

**ICEI - 2022 Conference Proceedings**

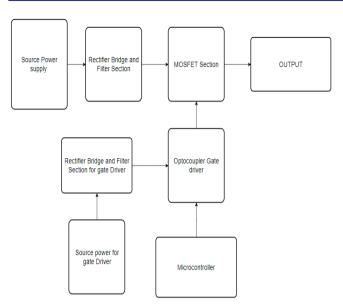

Fig (2) Hardware Diagram

The Block outline is rectifier channel circuit. Inverter switches DC over completely to AC. DC source battery is utilized to get steady DC source, yet for this situation consistent DC source is acquired by utilizing rectifier and channel. Rectifier is used for switching AC over completely to DC. To amend both half-patterns of a sine wave, the scaffold rectifier utilizes four diodes, associated together in a "span" setup. The discretionary bending of the transformer is related on one side of the diode length association and the stack on the contrary side. Throbbing DC is sent through channel and unadulterated DC is framed this unadulterated DC is shipped off MOSFET. By this interaction DC is switched over completely to AC this inverter circuit is only enhancer circuit and opto coupler TLP 250.

The microcontroller in the circuit is good for dealing with simply 5v anyway 12v Microcontroller is required, so the microcontroller is set off with PWM to get 12v, this is possible using opto coupler. Aftereffect of the opto coupler is extremely strengthened and sent through MOSFETs or PWM. Optocoupler is used to confine equipment to prevent electrical effect prospects or to bar unfortunate uproars. The diminished switch MLI furthermore makes seven outcome levels like standard H Bridge Multilevel inverter yet purposes 8 switches in light of which we can decrease trading hardships. The information voltage separator consists of 3 capacitors related in cascaded named C1, C2, & C3. Coming about to going across voltage separation the disengaged voltage then transferred to the H-range that is made utilizing Four diodes and MOSFETs. This voltage is next dispatch through H-stage to this result terminal that contains 4 MOSFET and from this the result will be seven level.

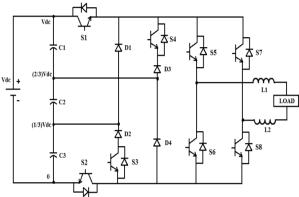

#### VI. REDUCED SWITCH MLI

The diminished switch Multilevel inverter comparatively makes seven result levels like normal H Bridge Multilevel inverter yet purposes eight switches due to this it can diminish exchanging difficulties. The below figure displays circuit of Multilevel inverter. This information voltage separator consists of 3 capacitors with cascade connection of C1, C2, and C3. Resulting to next dispatch through voltage separator this distributed is next dispatched through the H-length that is consisting of four diodes and MOSFETs. The voltage is transferred through H-extension to this result end that incorporates 4 MOSFET.

Fig (3) Circuit representation of MLI of seven level with diminished Switching configuration.

#### VII. OPERATION METHODOLOGY

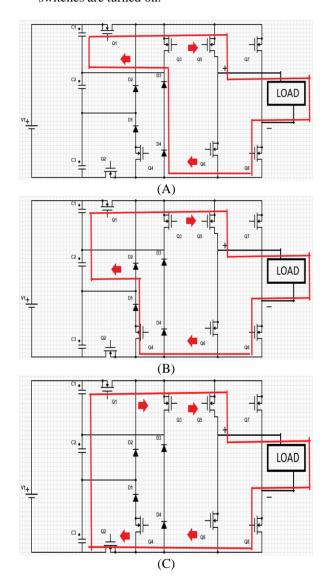

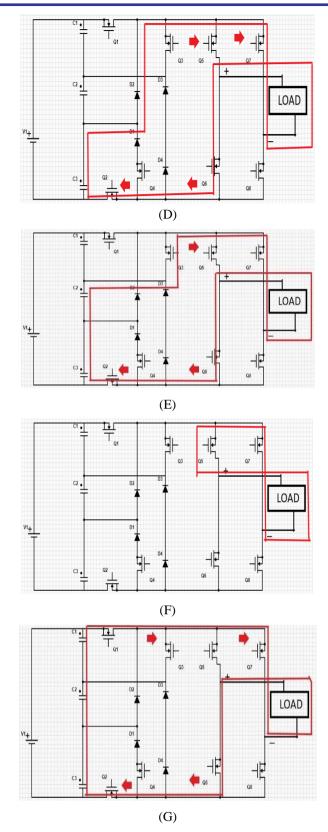

- Considering the information voltage (Vi), the seven levels acquired are: 0, \( \frac{1}{3} \) Vi, \( \frac{2}{3} \) Vi, \( \text{Vi}, \( -\frac{1}{3} \) Vi, \( -\frac{2}{3} \) Vi and - Vi. This turning out standard inasmuch as every voltage level is as per the going with, this displayed in below fig (3).

- Considering outcome voltage level ( $Vo = \frac{1}{3} Vi$ ), for the positive half cycle switch Q1 is turned on. Q5 & Q8 switches are moreover turned on & this energy is contributed by C1 Capacitor for instance (1/3 Vi).

- Considering outcome voltage level (Vo = ½Vi), Q1 & Q4 switches are turned on. This Q5 & Q8 switches too turned on & this energy is contributed by C1 & C2 capacitor for instance (2/3Vi).

- Considering outcome voltage level (Vo = Vi), Q1 & Q2 switches are turned on. This switches Q5 & Q8 too turned on & this energy is contributed by capacitor C1, C2 & C3 (Vi).

- Considering outcome voltage level (Vo = 1/3 Vi), for the negative half cycle switch Q2 is turned on. This Q6 & O7 switches are in like manner turned on & this energy is contributed by C3 capacitor for instance - 1/3 Vi

- Considering outcome voltage level (Vo = <sup>2</sup>/<sub>3</sub>Vi), Q2 & Q3 switches are turned on. This Q6 & Q7 switches too turned on & this energy is contributed by C3 & C2 capacitor (- <sup>2</sup>/<sub>3</sub>Vi).

- Considering outcome voltage level (Vo = Vi), Q2 & Q1 switches are turned on. This Q6 & Q7 switches too turned on & this energy is contributed by capacitor C1, C2 & C3 (- Vi).

- Considering outcome voltage level (Vo = 0), Q5 & Q7 switches are turned on.

Fig (4): Flow of current & position of Switches- (A) +1/3 Vi, (B) +2/3 Vi, (C) Vi (D) -1/3 Vi, (E) -2/3 Vi (F) -Vi (G) 0

#### VIII. SIMLUTION RESULTS

Fig (5) Simulation view

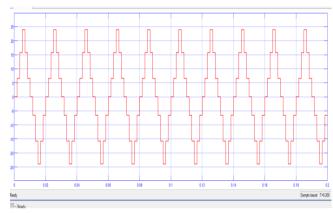

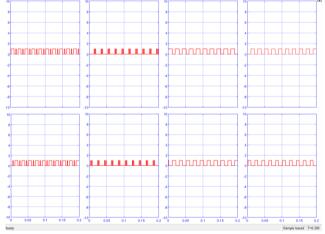

The Proposed 7 level inverter is simulated using matlab Simulink. Fig (6) and (7) shows the output voltage and current of proposed seven level inverter with reduces switches using Pulse width modulation which is

Table 1. Reduced switch MLI switching table

|           | 0 | 1 | 2 | 3 | 2 | 1 | 0 | 1 | 2 | 3 | 2 | 1 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|

| S1        | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| S2        | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| S3        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| <b>S4</b> | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| S5        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| <b>S6</b> | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| S7        | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| <b>S8</b> | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

Total switching sequence 12

50 Hz time is 1 sec as per 50HZ required

1 cycle time

$= 1 \sec / 50$

= 20 mili second

20 mili sec to micro sec = 20000

So Total delay in one cycle is 20000 micro second In each switching time required

20000/12

= 1666 Time delay

Time period = 1/f = 1/50 = 0.02

Pulse width = Switch ON position / Total no. of modes \* 100

Phase delay = Total Time period / Total no. of modes \* mode number

Fig (6) Output waveform

Fig (7) Waveform of PWM for all gates

#### IX. FUTURE SCOPE

This execution is a finished answer for staggered inverter. In this Implementation in future, we likewise can carry out Hardware with various source power moreover. In this plan we are utilizing one information power source. In future likewise we can execute for crossover framework. in future this execution will increment as we are carrying out this with advance way.

#### X. CONCLUSION

A staggered inverter is utilized in power change technique for, high power applications and high voltage an option for now, transportation frameworks, transmission framework and modern work drives and so on. Staggered inverters are hence observed to be entirely reasonable for the voltage drive activity. More significant level inverters give better execution when contrasted with lower-level inverters. Equipment we executed with atmega328 microcontroller. The result waveform tried in CRO in equipment project. Reenactment we are carrying out utilizing MATLAB reproduction instrument.

#### REFERENCES

- Krishna Kumar Gupta, Lalit Kumar, Shailendra Jain, International journal of Institute of Electrical and Electronics Engineers on conference A new seven level hybrid Inverter. 2012

- [2] Abhishek Kumar Ranjan, International Conference on Circuit, Power and Computing Technologies [ICCPCT].2015

- [3] Niraj Vijayshankar Mishra, International Journal of Creative Research Thoughts (IJCRT).2015

- [4] Mahammed Sameer m Attar, International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering. 2016

- [5] Vanya Goel, Jagdish kumar, Jaimala Gambhir, A seven level multilevel inverter topology with improved results using PWM technique, (IEEE), 2016

- [6] Ruhina R. Shaikh, Prof. J.R. Rana, Microcontroller Based Single-Phase Seven-Level Inverter for Photo-Voltaic System (IRJET). 2016

- [7] Ruhina R. Shaikh, Single Phase Seven Level Inverter (IEEE), Execution of the single stage 7 level inverter with PWM control plot. 2016

- [8] Prof. C.S. Sharma, Rahul Tamrakar Associate Professor, 2Research Scholar Department of electrical engineering Samrat Ashok Technological Institute Vidisha, Madhya Pradesh. 2016

- [9] Jyoti M. Kharade, International Journal of Innovative Research in Science, Engineering and Technology.2017

- [10] Sze Sing Lee, A Single-Phase Single-Source 7-Level Inverter with Triple Voltage Boosting Gain, IEEE.2018

- [11] Wahyu Mulyo Utomo, Afarulrazi, International Journal of Engineering & Technology. Staggered inverter utilizing 7-level Cascaded H-Bridge of staggered DC-AC inverter. 2018

- [12] Niraj Vijayshankar Mishra, International Journal of Creative Research Thoughts (IJCRT).2020

- [13] Shreya Bandill, Sadbhawna Kushwaha2, Shivani Soni3, Yogita Rathode4, 7- level cascaded h-bridge multilevel inverter (IRJET). 2020

- [14] Sze Sing Lee, A Single-Phase Single-Source 7-Level Inverter with Triple Voltage Boosting Gain, IEEE.2020

- [15] Abhishek Kumar Ranjan, International Conference on Circuit, Power and Computing Technologies [ICCPCT].2020