# Power Stress Reduction In Single-Stage Power Factor Correction By AC/DC Fly Back Converter

P.VEERAMANITHANGAM<sup>1</sup>, P.GANESH<sup>2</sup>, R.KALAIARASI<sup>3</sup>, T.MANOKARAN<sup>4</sup>

<sup>1, 2, 3</sup>PG Scholar II year PED, Department of Electrical and Electronics Engineering,

Sri Subramanya College of Engineering and Technology,

Sukkamanaikanpatti Palani, Dindigul, India.

<sup>4</sup>Department of Electrical and Electronics Engineering,

Sri Subramanya College of Engineering and Technology,

Sukkamanaikanpatti, Palani, Dindigul, India.

## Abstract

This paper discusses the major issues that exist in the single-stage ac/dc converters with power factor correction (PFC) and presents a novel converter based on a quasi-active PFC scheme. Two additional windings wound in the transformer of a conventional dc/dc fly back converter are used to drive and achieve continuous current mode operation of an input inductor. In addition, direct energy transfer paths are provided through the additional windings to improve the conversion efficiency and to reduce the dc bus capacitor voltage below 450 V for universal line applications. The proposed converter can be easily designed to comply with IEC 61000-3-2 Class D requirement and to achieve fast output voltage regulation. By properly tuning the converter parameters, a good tradeoff between efficiency, dc bus capacitor voltage stress, and harmonic content can be achieved. Operating principles, analysis, and experimental results of the proposed method are presented.

## 1. Introduction

RECENTLY, many high-frequency active power factor correction(PFC) topologies and current shaping techniques for ac/dc converters have been developed [1] to meet standards such as IEC 61000-3-2. In conventional converter design, a two stage scheme was usually employed insimultaneously performing PFC and fast output regulation by using two independent

controllers and optimized power stages. However, the cost and complexity of the converter increases with the increased component count. A cost-effective solution known as a singlestage PFC (S2PFC) converter was developed, in which the PFC stage and the dc/dc converter are combined into one stage [2]–[4]. These S2PFC converters usually use a boost converter to achieve PFC with discontinuous conduction mode (DCM) operation. A detailed review of the S2PFC topologies using DCM boost converter is presented in [3].Some other integrated S2PFC schemes are also implemented using DCM buck-boost or buck converter [5]–[9]. Generally, the power factor (PF) of a conventional two-stage converter is much higher than the single-stage scheme. However, the input current harmonics of S2PFC converters still can meet the regulatory standards. Although the single-stage scheme is attractive in low-cost and low-power applications due to its simplified power stage and control circuit, major drawbacks such as low efficiency, high dc bus voltage stress, and working in DCM of the input PFC stage still exist. The DCM operation gives a lower total harmonic distortion (THD) of the input current compared to the continuous current mode (CCM). On the other hand, the CCM operation yields a slightly higher efficiency compared to the DCM operation [19].

To overcome the drawbacks of the single-stage scheme, several converters with input currentshaping have been presented [10], [11], in which a high-frequency ac voltage source is connected in series with the rectified input voltage to shape the input current. The variable switching frequency control technique that

is proposed in [12] can reduce the dc bus voltage stress. The method is unable to suppress the dc bus voltage below 450 V for universal line applications (100–240 V ac), and it complicates the design of the inductive components due to the wide-range switching frequency operation. Some alternative designs using additional coupled feedback windings are introduced in [13]–[20], wherein the dc bus capacitor voltage is reduced below 450 V. Nevertheless, the feedback windings also induce a dead angle in the input current, hence resulting in a high line current distortion. The coupled feedback winding concept is also implemented using a center tap transformer and a synchronous rectifier to improve the PF and efficiency [21]. The converter is operated at the boundary of the DCM and CCM using a variable frequency controller to reduce the switching turn-on loss. In addition, a dead angle still exists in the input current wave form. The topologies proposed in [22] and [23] overcome the dc bus capacitor voltage stress using the parallel PFC concept.

In this paper, a new quasi-active PFC circuit is presented. The circuit is based on adding two auxiliary windings coupled to the transformer of a cascaded dc/dc flyback converter. The PFC cell is placed between the input rectifier and the low-frequency filter capacitor, capacitor, which is a similar approach to the conventional activePFC design but without an active power switch. Since the dc/dc converter is operated at high switching frequency, the auxiliary windings produce a high-frequency pulsating source such that the input current conduction angle is lengthened and the input current harmonics is reduced. Furthermore, the high-frequency pulsating source requires smaller size components, resulting to a lower cost. The input inductor current can be designed to operate in CCM. By properly designing the converter parameters, a good tradeoff between efficiency, dc bus capacitor voltage stress, and harmonic content can be achieved. The structure and operating principles of the proposed converter are presented in Section II. The design example and the experimental results are presented in Section III. Section IV gives the conclusion.

## 2. Proposed Quasi-Active PFC Circuit

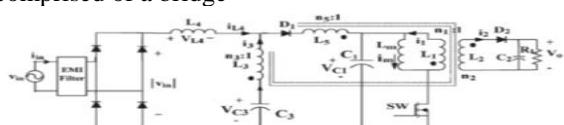

The proposed quasi-active PFC circuit is discussed in this section. As shown in Figure 1, the circuit is comprised of a bridge

Figure 1. Proposed quasi-active PFC circuit diagram.

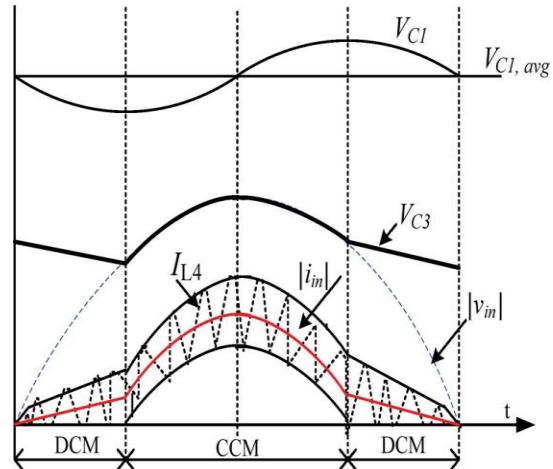

Figure 2. Input inductor current  $IL4$  illustrating its conduction modes during half line current period.

rectifier, a boost inductor  $L4$ , a capacitor  $C3$ , an intermediate dc bus capacitor  $C1$ , and a discontinuous input current power load (a DCM fly back converter in this case). Two auxiliary windings  $L3$  and  $L5$  are added to the primary side of the transformer in order to shape the input current. In the proposed quasi-active PFC scheme, the dc/dc converter section is not directly involved in the PFC; it simply offers a driving power by applying a series of discontinuous current pulses. Compared to the circuit reported in [35], the proposed circuit shown in Figure 1 is different in two ways: the dotted convention of the third winding ( $L3$ ) of the fly back transformer is reversed, and an additional winding  $L5$  is inserted. If the third winding ( $L3$ ) is wound such that the dotted terminal of  $L3$  is similar to  $L1$  and  $L5$  and opposite to the secondary winding  $L2$ , the circuit operation and analysis will be fundamentally different. Consequently, these changes will be reflected mainly on the input inductor  $L4$  which operates in CCM/DCM, as shown in Figure 2. Compared to [35], the input inductor always operates in DCM. Although the DCM gives lower THD of the line current, however, CCM operation required a smaller EMI filter, and the harmonic content of the line current can still be maintained below the IEC 61000-3-2 Class D requirements. Furthermore adding the winding  $L5$  in the proposed circuit offers more flexibility in maintaining the dc bus capacitor voltage  $VC1$  well below 450 V for universal line flexibility in maintaining the dc bus capacitor voltage  $VC1$  well below 450 V for universal line applications. As a result, the voltage stress across the power switch can be reduced. In addition, two direct energy transfer paths are provided by the two feedback windings, which can improve the conversion efficiency. When the switch is

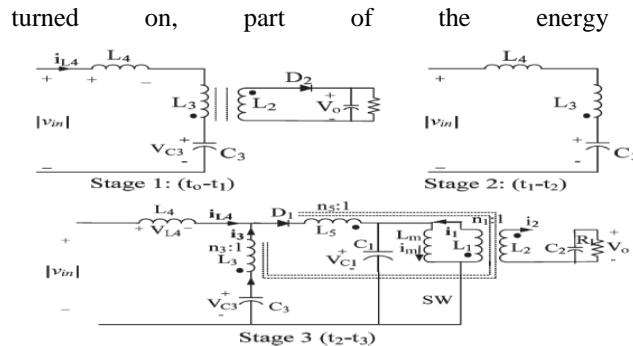

Figure 3. Equivalent circuits for the three stages of operation of the proposed pfc circuit

rom the input inductor is directly transferred to the transformer. When the switch is turned off, part of the energy from the input is transferred to the secondary output capacitor through the winding  $L_3$ . As a result, the conversion efficiency is expected to remain high, as achieved in Furthermore, the size of the capacitor  $C_3$  in series with the winding  $L_3$  is smaller

To simplify the analysis, the following assumptions are made.

- 1) All semiconductor components are ideal.

- 2) The power transformer is ideal (no leakage flux).

- 3) The voltages across the capacitors are constant.

- 4) The switching frequency is much higher than the line frequency. Therefore, the input voltage is constant during a switching cycle.

## 2.1. Operation stages

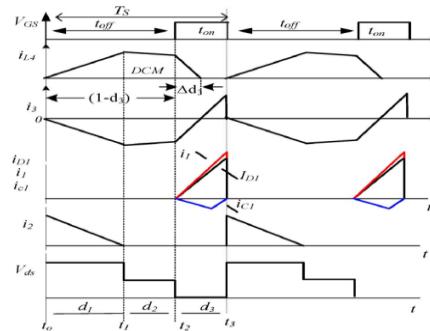

This section presents the principle of operation of the proposed PFC circuit. A typical input inductor current produced by the circuit is shown in Figure 2. It can be seen that, during a half cycle of the supply, the waveform of the input current  $i_{L4}$  always has two parts, namely, the DCM and CCM parts. When  $|v_{in}| < VC_3$ , the current  $i_{L4}$  is low, and hence, the input inductor  $L_4$  operates in DCM. With the increase of the input voltage such that  $|v_{in}| \geq VC_3$ , the inductor current increases and becomes continuous (CCM). At steady state, the topology has three operating stages, as shown in Figure 3. The key switching waveforms for both CCM and DCM parts are shown in Figs. 4 and 5, respectively.

*Stage 1 (t<sub>0</sub>–t<sub>1</sub>):* At  $t = t_0$ , the switch (SW) is turned off, and diode  $D_1$  is reverse biased due to  $(VC_1 + VL_5)$ , which is always higher than  $|v_{in}|$ . The inductor  $L_4$  absorbs energy from the input source, and therefore, the current  $i_{L4}$  is increased linearly. During this stage, the capacitor  $C_3$  is charging. Meanwhile, diode  $D_2$  is forward biased, and the load absorbs energy from both the magnetizing inductor through primary winding  $n_1$  and the input voltage through the

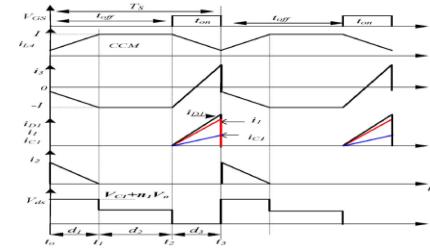

Figure 4. Key switching waveforms of the proposed PFC with CCM operation

Figure 5. Key switching waveforms of the proposed PFC with DCM operation.

period. As a result, the efficiency is improved. This stage ends when the secondary current  $i_2$  becomes zero at ( $t = t_1$ )

*Stage 2 (t<sub>1</sub>–t<sub>2</sub>):* During this stage, the switch (SW) and both diodes  $D_1$  and  $D_2$  are turned off. The input current continues to flow through the circuit formed by  $|v_{in}|$ ,  $L_4$ ,  $L_3$ , and  $C_3$ . The capacitor  $C_3$  is still charging at this stage. The current  $i_{L4}$  slightly decreases when  $|v_{in}| < VC_3$  (for DCM part) and is constant when  $|v_{in}| \geq VC_3$  (for CCM part). This stage ends when the switch (SW) is turned on at  $t = t_2$ .

*Stage 3 (t<sub>2</sub>–t<sub>3</sub>):* At  $t = t_2$ , the switch (SW) is turned on, and diode  $D_1$  is conducting. Therefore, the stored energy in  $L_4$  and  $C_3$  is transferred to the primary windings  $n_1$  and  $n_5$ , so more energy is stored in the magnetizing inductor of the transformer. Hence, the primary winding current increases linearly. In addition, when  $|v_{in}| < VC_3$  (DCM part), the dc bus capacitor  $C_1$  discharges its energy to the transformer primary winding. Note that, because  $|v_{in}|$  is low, the current  $i_{L4}$  will decrease to zero (DCM) before the switch is turned off. Once  $i_{L4} = 0$ , the capacitors  $C_3$  and  $C_1$  continue to supply the energy to the primary windings of the transformer. However, when  $|v_{in}| \geq VC_3$  (CCM part), the input voltage is high enough such that it can provide most of the energy to the primary windings  $n_1$

$$P_0 = \frac{V_{C1}^2}{2L_m} d_3^2 T_s \quad (15)$$

In a half line cycle, the input energy is equal to the output energy at steady state such that  $P_{in} = P_0$ . Therefore, the dc bus capacitor voltage is written as

$$v_{c1} = v_m \sqrt{\frac{n_3}{n_1 - n_3 + n_5} \times \frac{L_m}{2L_4} \frac{n_3 - n_5}{n_1}} \quad (16)$$

From (16), it can be seen that the dc bus voltage  $V_{C1}$  is independent from the load changes, and it is a function of the inductance values, turn ratios, and input voltage. Therefore, high voltage stress can be overcome by properly designing the ratio of the inductance ratio  $L_m/2L_4$  and the number of turns  $n_1$ ,  $n_3$ , and  $n_5$ .

### 3. Design Example and Experimental Results

The performance of the new quasi-active PFC circuit shown in Figure 1 was designed and experimentally verified. The main design objectives of the proposed circuit can be divided into two directions. First, it achieves low THD of the line current to comply with the IEC 61000-3-2 Class D standard with a CCM operation of the input inductor ( $L_4$ ) as much as possible. Second, it limits the voltage stress of the dc bus capacitor  $V_{C1}$  below 450 V for a universal input voltage (100–240 Vac). From the preceding analysis in Section II, assuming that the secondary winding  $n_2 = 1$ , it is found that the number of turns ( $n_1$ ,  $n_3$ , and  $n_5$ ) and the inductors ratio  $L_m/2L_4$  are the key design parameters. Specifically, the turns ratio ( $n_3/n_1$ ) has a significant impact on both the quality of the input current and the dc bus capacitor voltage. The DCM flyback converter was designed for  $V_{in,rms}$  (100–240 V),  $V_o = 50$  V, and output power of 80 W, and the overall efficiency of 86% is assumed. The switching frequency is 100 kHz, and the maximum duty cycle is 0.45

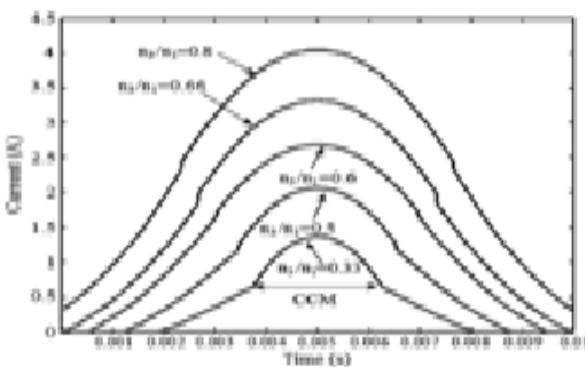

Fig 6. Average input current waveform for a half line cycle and difference turns ratio ( $\frac{n_3}{n_1}$ )

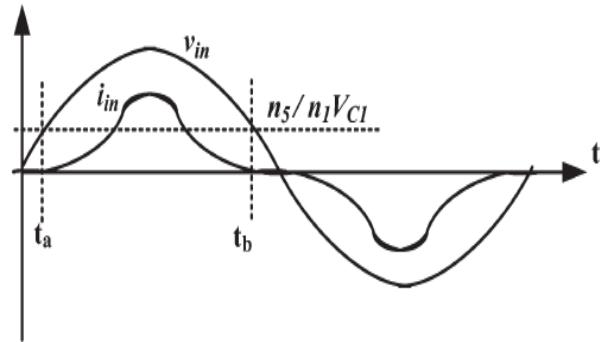

Figure 7. Input voltage and current waveforms showing the effect of the number of turns  $n_5$

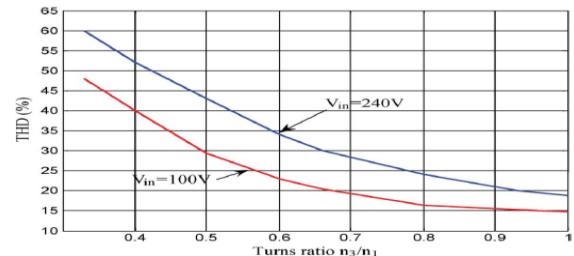

Figure 8. THD of the input current as a function of the turns ratio ( $n_3/n_1$ ).

Based on (8) and (9), Figure 6 shows the average input current waveform for a half line cycle as a function of the turns ratio ( $n_3/n_1$ ) for an input voltage of 100 V. It is assumed that all of the other parameters are constant. It can be seen that, to reduce the dead angle of the input current and to provide a continuous current flow, the turns ratio ( $n_3/n_1$ ) must be greater than or equal 0.5. In addition, the number of turns  $n_5$  also affects the dead time of the input current, as shown in Figure 7. The higher the number of turns ( $n_5$ ) is, the bigger the dead time will be. Therefore, the turns ratio ( $n_3/n_1$ ) and ( $n_5$ ) must also be selected such that the input current delay times ( $t_a$  and  $t_b$ ) are approximately equal to zero. Figs. 8 and 9 show the calculated

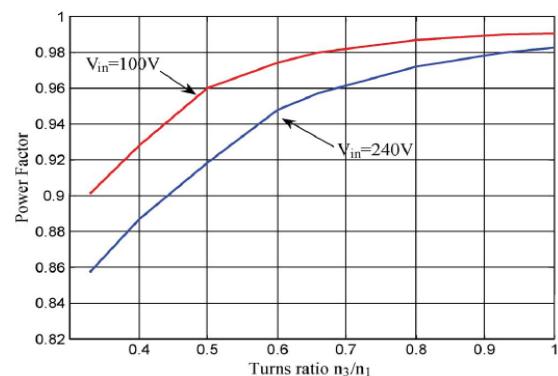

Figure 9. Input PF as a function of the turns ratio ( $n_3/n_1$ ).

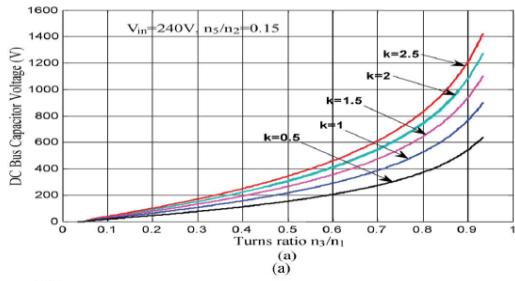

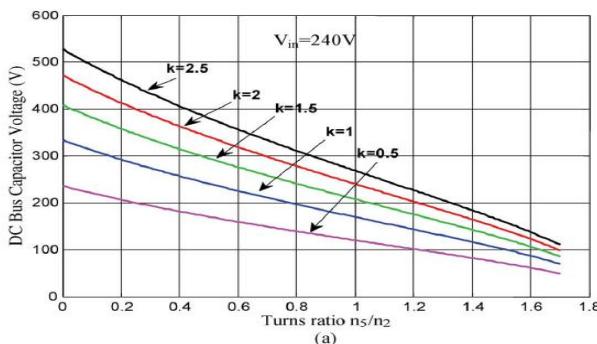

Fig. 9. Input PF as a function of the turns ratio ( $n_3/n_1$ ).Figure 10. Calculated dc bus capacitor voltage versus turns ratio ( $n_3/n_1$ ) for  $V_{in} = 240$  V. (a)  $n_5/n_2 = 0.15$ . (b)  $n_5/n_2 = 0.3$ .

THD and PF of the input current as a function of the turns ratio ( $n_3/n_1$ ) for input voltages of 100 and 240 V. It can be observed that the turns ratio ( $n_3/n_1$ ) controls the quality of the input current. The higher the turns ratio is, the lower is the THD, and the higher is the PF obtained. However, based on (16), a higher

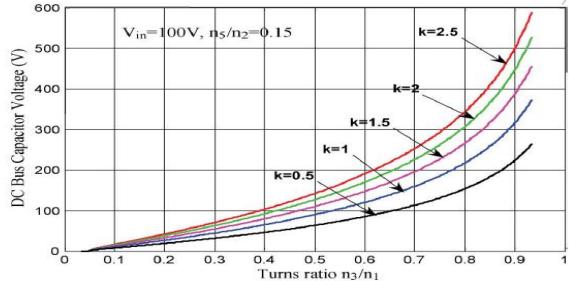

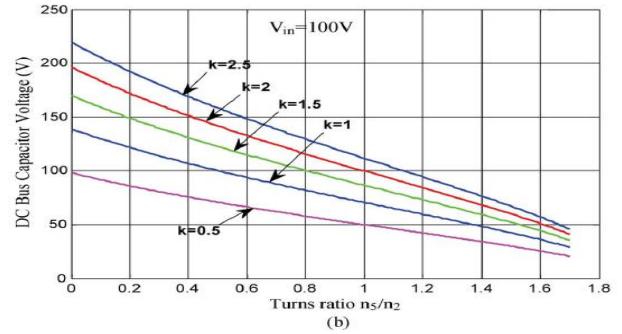

Figure 11. Calculated dc bus capacitor voltage versus turns ratio ( $n_3/n_1$ ) for  $V_{in} = 100$  V.Figure 12. Turns ratio  $n_5/n_2$  with  $n_3/n_1 = 0.6$ . (a)  $V_{in} = 240$  V. (b)  $V_{in} = 100$  V.

turns ratio ( $n_3/n_1$ ) means a higher dc bus capacitor voltage( $VC_1$ ) stress. Figure 10–12 show the relationship between the dc bus capacitor voltage and circuit parameters, turns ratio ( $n_3/n_1$ ) and ( $n_5/n_2$ ), and inductance ratio ( $k = L_m/2L_4$ ) for input

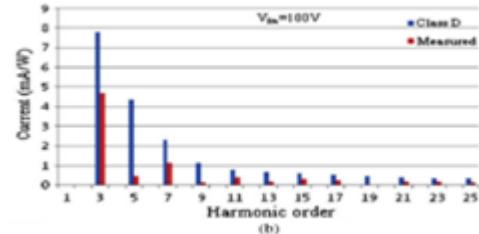

Figure 13. (a) Measured input voltage ( $V_{in}$ ; 100/Div) and filtered input current( $I_{in}$ ; 1 A/Div) for  $V_{in} = 100$  V. (b) Corresponding harmonics content(THD = 22%).

Voltages of 240 and 100 V, respectively. It is shown in Figs. 10 and 11 that, for a given value of  $k$  and  $n_5$ , if the turns ratio  $n_3/n_1 > 0.6$ , the relationship between the dc bus capacitor voltage and the turns ratio becomes nonlinear, and a small change in the turns ratio results in a very high capacitor voltage stress. Therefore, a tradeoff between the input current quality and the dc bus capacitor voltage must be made. For a universal input voltage, the maximum capacitor voltage must be limited to 450 V. Therefore, in Figs. 6 and 8–11, for the range of  $k = 1–2$  and for a turns ratio value of  $n_5/n_2$ . Finally, Figure 12 shows the relationship between the turns ratio  $n_5/n_2$  and the dc bus capacitor voltage ( $VC_1$ )

for a turns ratio  $n3/n1 = 0.6$ . It can be seen that, for given values of  $k$  and turns ratio ( $n3/n1$ ), a higher turns ratio ( $n5/n2$ ) leads to a lower capacitor voltage ( $VC1$ ). However, a higher turns ratio ( $n5/n2$ ) may induce a dead time in the input current, as shown in Figure 7. Therefore,  $k = 2$  and  $n3/n1 = 0.6$  and  $n5/n2 = 0.2$  are selected in this design, which ideally give  $VC1 \approx 408$  V for  $V_{in} = 240$  V. However, practically, the voltage  $VC1$  could be lower due to unavoidable circuit losses. In addition, a capacitor with a voltage rating of 450–500 V could be used since it is available in the market. The conventional fly back transformer is constructed with the number of turns  $n1 = 46$ ,  $n2 = 15$ ,  $n3 = 28$ , and  $n5 = 3$  and magnetizing inductance  $Lm = 200 \mu\text{H}$ . The input inductor  $L4 = 50 \mu\text{H}$ . The capacitor values are selected as  $C1 =$

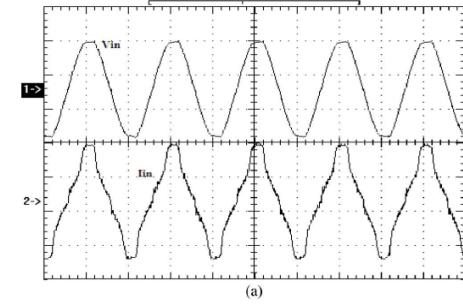

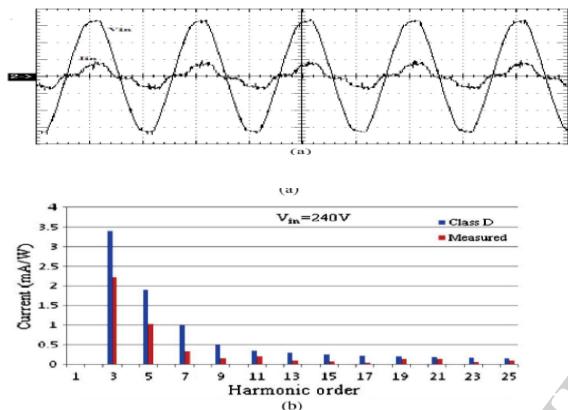

Fig 14. Measured input voltage (v in ;100/div) and filtered input current(b)corresponding harmonic current

Fig 15. Measured waveforms for  $V_{ds}$  (switch voltage) 47  $\mu\text{F}/500$  V and  $C2 = 2 \times 470 \mu\text{F}$ .

Assuming that  $\Delta Vc3 = 100$  V,  $P_{in, min} = 15$  W,  $V_{rms} = 240$  V (worst cases cenario) ,  $t = 10$  ms (half of the half line period for discharge),and then  $C3 \leq 6.25 \mu\text{F}$ . Therefore,  $C3 = 4.7 \mu\text{F}/450$  V is selected such that  $VC3$  follows the input voltage, and the capacitor has to be discharged much faster than the 50-Hz input. Based on the aforementioned design example, the converter was built using the following components: the diode bridge = KBU8J,  $D1 = \text{MUR1560}$ ,  $D2 = \text{MUR1510}$ , and  $SW = \text{SPW22N60C3}$ . Figure 13(a) shows the measured waveforms of the input voltage and input current for a100-Vac input voltage. The harmonic content of the input current compared to Class D regulation

standard is shown in Figure 13(b). Similarly, Figure 14(a) and (b) shows the

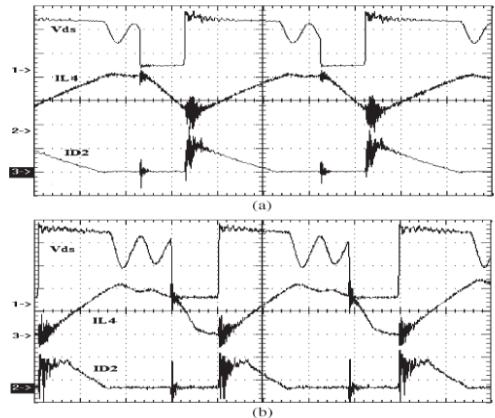

Figure 16. Measured waveforms for  $V_{ds}$  (switch voltage),  $IL4$ , and  $ID2$ . (a) CCM operation. (b) DCM operation

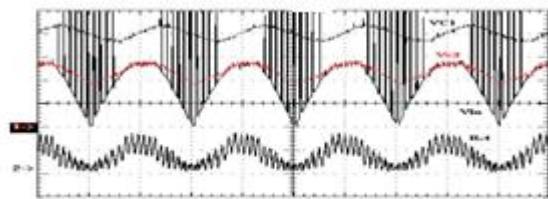

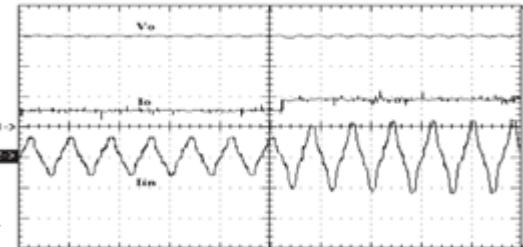

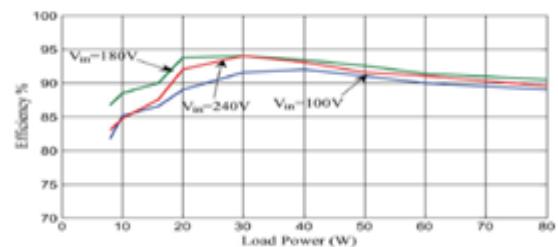

Fig 17. Transient response for a step load change measured input voltage, input current, and harmonic content for  $V_{in} = 240$  V. It can be observed that the standard specification IEC 61000-3-2 Class D is easily fulfilled. Figure 15 shows the measured waveforms of the rectified input voltage, capacitor voltage  $C3$ , dc bus voltage  $VC1$ , and input inductor current  $IL4$ . It can be observed that, when  $/v_{in}/ < VC3$ , the inductor current is in DCM, and when  $/v_{in}/ = VC3$ , the current is in CCM. Figure 16(a) and (b) shows the key waveforms of the switch voltage ( $V_{ds}$ ), input inductor current  $IL4$ , and output diode current  $ID2$  for both operation modes, i.e., CCM and DCM, respectively. Figure 17 shows the transient response of the converter for a step change of load from 50% to 100%. As can be observed, a fast dynamic response is obtained. Figure 18 shows the measured efficiency of the converter for a range of loads and three different input voltages. It can be observed from the figure that the efficiency of the converter is above 85% for higher loads.

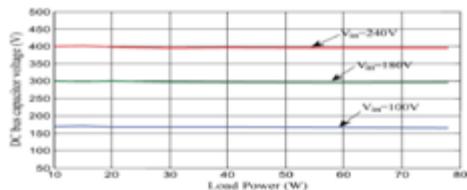

Figure 18. DC bus capacitor voltage  $VC_1$  versus load power for different input voltages.

Figure 18 shows the measured dc bus capacitor voltage  $VC_1$  for a range of load and input voltage variations. It can be seen that the capacitor voltage can be maintained below 450 V by properly designing the number of turns ( $n_1$ ,  $n_3$ , and  $n_5$ ) and the inductors ratio ( $k$ ). Finally, Table I summarizes the comparison of several single-stage ac/dc converters presented in [13]–[15], [19], [21], [25], and [32] with the proposed converter in terms of circuit implementation and performance. The main advantage of the proposed converter over the topologies presented in Table I is that the proposed converter presents a high-quality CCM input current with the lowest THD = 22%. Usually, in a single-stage converter, there is always a tradeoff between the CCM operation and THD of the line current, where, by the CCM operation, it usually causes high harmonic current. Furthermore, in all of the published approaches listed in the table, increasing the turns ratio of  $N_{au}/N_{pc}$  can reduce the input PF by inducing a dead angle in the line current, whereas in the proposed converter, the higher the turns ratio  $n_3/n_1$  is, the higher is the PF. However, the turns ratio cannot be arbitrarily large because of the maximum limit of the dc bus capacitor voltage. The maximum dc bus capacitor stress is  $VC_1 = 400$  V for the proposed converter, and it can be maintained always below 450 V by properly selecting the number of turns ( $n_1$ ,  $n_3$ , and  $n_5$ ) and the inductors ratio  $L_m/L_4$ . Although the dc bus voltage stress in the circuits presented in [14], [15], [19], [21], and [25] is lower than 400 V, those solutions penalized the current quality with high THD. The proposed converter can also be designed to achieve a dc bus voltage stress which is lower than 400 V, but the THD of the input current will increase slightly due to a small dead angle in the input current waveform. Therefore, the design parameters are optimized to maintain a low THD without any dead angle and to limit the capacitor voltage stress below 450 V. In addition, the proposed converter achieves a high efficiency (>82%) due to the DPT paths provided by the two auxiliary windings. The conversion efficiency in [15] and [21] is almost similar to the proposed converter. Nevertheless, their harmonic currents are considerably higher, and they also require a variable frequency control.

## 4. Conclusion

In this paper, a new quasi-active PFC circuit has been presented. In the proposed scheme, auxiliary windings are added to the transformer of a dc/dc DCM flyback converter. Since the dc/dc converter is operated at high switching frequency, the auxiliary windings produce a high-frequency pulsating source such that the input current conduction angle is lengthened and the input current harmonics are reduced. The input inductor can operate in DCM+CCM. The single-stage PFC circuit has high efficiency when it operates in CCM. Hence, by properly designing the converter parameters, a high efficiency can be obtained while maintaining the total current harmonic content well below the IEC 61000-3-2 Class D standard specifications. The operating principles, analysis, and experimental results of the proposed method have been presented.

## References

- [1] O. Garcia, J. A. Cobs, R. Prieto, and J. Uceda, "Single-phase powerfactor correction: A survey," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 749–755, May 2003.

- [2] R. Redl, L. Balogh, and N. O. Sokal, "A new family of single-stage isolated power factor correctors with fast regulation of the output voltage," in *Proc. IEEE Power Electron. Spec. Conf.*, 1994, pp. 1137–1144.

- [3] C. Qian and K. Smedley, "A topology survey of single-stage power factor with a boost type input-current-shaper," *IEEE Trans. Power Electron.*, vol. 16, no. 3, pp. 360–368, May 2001.

- [4] G. Moschopoulos and P. Jain, "Single-phase single-stage power-factor-corrected converter topologies," *IEEE Trans. Ind. Electron.*, vol. 52, no. 1, pp. 23–35, Feb. 2005.

- [5] M. A. Al-Saffar, E. H. Ismail, and A. J. Sabzali, "Integrated buck-boost quadratic buck PFC rectifier for universal input applications," *IEEE Trans. Ind. Electron.*, vol. 24, no. 12, pp. 2886–2896, Dec. 2009.

- [6] J. M. Alonso, M. A. Dalla Costa, and C. Ordiz, "Integrated buck-flyback converter as a high-power-factor off-line power supply," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1090–1100, Mar. 2008.

- [7] D. Gacio, J. M. Alonso, A. J. Calleja, J. García, and M. Rico-Secades, "A universal-input single-stage high-power-factor power supply for HB-LEDs based on integrated buck-flyback converter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 2, pp. 589–599, Feb. 2011.

- [8] H. L. Cheng, Y. C. Hsieh, and C. S. Lin, "A novel single-stage high-power-factor ac/dc converter featuring high circuit efficiency," *IEEE Trans. Ind. Electron.*, vol. 58, no. 2, pp. 524–532, Feb. 2011.

- [9] I. Takahashi and R. Y. Igarashi, "A switching power supply of 99% power factor by dither rectifier," in *Proc. IEEE Int. Telecommun. Energy Conf.*, 1991, pp. 714–719.

- [10] T. F. Wu, T. H. Yu, and Y. C. Liu, "An alternative approach to synthesizing single-stage converters with power factor correction feature," *IEEE Trans. Ind. Electron.*, vol. 46, no. 4, pp. 734–748, Aug. 1999.

- [12] M. M. Jovanovic, D. M. Tsang, and F. C. Lee, "Reduction of voltage stress in integrated high-quality rectifiers-regulators by variable-frequency control," in *Proc. IEEE APEC Conf.*, 1994, pp. 569–575.

- [13] J. Qian, Q. Zhao, and F. C. Lee, "Single-stage single-switch power factor correction ac/dc converters with dc-bus voltage feedback for universal line applications," *IEEE Trans. Power Electron.*, vol. 13, no. 6, pp. 1079–1088, Nov. 1998.

- [14] Q. Zhao, F. C. Lee, and F. S. Tsai, "Voltage and current stress reduction in single-stage power factor correction ac/dc converters with bulk capacitor voltage feedback," *IEEE Trans. Power Electron.*, vol. 17, no. 4, pp. 477–484, Jul. 2002.

- [15] H. Ma, Y. Ji, and Y. Xu, "Design and analysis of single-stage power factor correction converter with a feedback winding," *IEEE Trans. Power Electron.*, vol. 25, no. 6, pp. 1460–1470, Jun. 2010.

- [16] L. Huber, J. Zhang, M. Jovanovic, and F. C. Lee, "Generalized topologies of single-stage input-current-shaping circuits," *IEEE Trans. Power Electron.*, vol. 16, no. 4, pp. 508–513, Jul. 2001.

- [17] P. Das, S. Li, and G. Moschopoulos, "An improved ac–dc single-stage fullbridge converter with reduced dc bus voltage," *IEEE Trans. Ind. Electron.*, vol. 56, no. 12, pp. 4882–4893, Dec. 2009.

- [18] J. Sebastian, A. Fernandez, P. Villegas, M. Hemando, and J. Prieto, "New active input current shapers to allow ac-to-dc converters with asymmetrically driven transformers to comply with the IEC-1000-3-2," *IEEE Trans. Power Electron.*, vol. 17, no. 4, pp. 493–501, Jul. 2002.

- [19] L. Huber and M. Jovanovic, "Single-stage single-switch isolated power supply technique with input-current-shaping and fast output-voltage regulation for universal input-voltage-range applications," in *Proc. IEEE APEC*, Feb. 1997, pp. 272–280.

- [20] J. A. Villarejo, J. Sebastián, F. Soto, and E. de Jódar, "Optimizing the design of single-stage power-factor correctors," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1472–1482, Jun. 2007.

- [21] J. J. Lee, J. M. Kwon, E. Ho Kim, W. Y. Choi, and B. H. Kwon, "Singlestage single-switch PFC flyback converter using a synchronous rectifier," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1352–1365, Mar. 2008.

- [22] O. Garcia, J. A. Cobos, R. Prieto, and J. Uceda, "Simple ac/dc converters to meet IEC1000-3-2," in *Proc. IEEE Annu. Meeting APEC*, 2000, pp. 487–493.

- [23] N. Vazques, C. Hernandez, R. Cano, J. Antonio, E. Rodrigues, and J. Arau, "An efficient single-switch