# Performance Analysis of Energy Efficent Advanced Encryption Standard

Prof. P. C.Warule Dept. of Electronics and Telecommunication Engineering PREC, Loni Pune, Maharashtra, India Prof. R. N. Kadu Dept. of Electronics and Telecommunication Engineering PREC, Loni Pune, Maharashtra, India Prof. V. A. Aher Dept. of Electronics and Telecommunication Engineering PREC, Loni Pune, Maharashtra, India

Abstract— Execution assessment of the Advanced Encryption Standard hopefuls has ended up prompted concentrated investigation of both equipment and programming usage. In any case, number of articles present different execution results, it demonstrates that proficiency could be extraordinarily enhanced by applying successful configuration rules adjusted to gadgets and calculations. This paper indicates different methodologies for effective usage of the Advanced Encryption Standard calculation. For various uses of the AES calculation might require distinctive velocity/territory tradeoffs, we propose an essential study to the conceivable execution plans, additionally the talk of configuration system and algorithmic advancement so as to enhance past reported results. We propose a framework to assess equipment proficiency at various strides of the outline process. We likewise utilize an ideal pipeline that considers the spot and course imperatives. Coming about circuits fundamentally enhance the past reported results, throughput is upto 18.5 Gbits/sec and the territory necessities can be constrained up to 542 cuts and 10 RAM hinders with a proportion throughput/region enhanced by least 25% of the best-known plans in the Xilinx Virtex-E innovation.

Keywords— EDK, EDK, Real time Communication, AES, Security

# BACKGROUND

The Advanced Encryption Standard determines a cryptographic calculation that can be utilized to secure an electronic information. AES calculation is unbalanced square figure that can encode (encipher) and decode (translate) data. an indiscernible type of information changed over by an encryption called figure message and unscrambling the figure content changes over the information once more into its unique structure, called as plaintext.

The AES after the Data Encryption Standard was discovered excessively frail due to its little key size and the mechanical progressions in processor force and vitality necessities. Fifteen hopefuls were acknowledged and taking into account open remarks the pool was diminished to five. One of these five calculations was chosen as anticipated standard: a marginally altered adaptation of the Rijndael.

The Rijndael, whose name depends on the names of its two Belgian designers, names are Vincent Rijmen& Joan Daemen is a Block figure, which implies it takes a shot at altered length gathering of bits, which are called pieces. It takes an info piece of a specific square size, normally 128 bits, and produces a relating yield square of the same size. The change utilizes a second information, which is mystery key with lengths of 128, 192 and 256 bits variable. Not at all like DES, which depends on Feistel system, AES is a substitution-stage system, which is a progression of numerical operations that utilization substitutions (additionally called S-Box) and changes (P-Boxes) and their watchful definition expresses that every yield bit relies on upon each data bit.

# BLOCK CIPHER

When a *block cipher* algorithm used for encryption as well as decryption purposes, the message is divided into the blocks of bits. All blocks are then goes through the various routine like substitution, transposition, other mathematical functions.

The algorithm decides all the possible functions which are available to be used on the message & the key which determines in what order these functions will take place. Strong algorithms tries to figure out all the functions that take place on the message which are basically impossible.

# ADVANTAGES OF AES:

- In AES, input messages of length 128 bits which is more than the DES.

- AES has the variable secret key lengths such as 128 bits, 192 bits and 256 bits, whereas the DES and Triple DES have fixed length of 64 bits.

- The cipher key is expanded into the larger key, which is then later used for the actual operation.

- The Expanded Key will be derived from the Cipher Key and never be specified directly.

- AES algorithm is very hard to attack or crack when compared with DES.

- AES will be faster than to the Triple DES.

# APPLICATION

- In High speed applications like ATM/Ethernet/Fiber-Channel switches

- In Secure video teleconferencing

- In Routers and Remote Access Servers

# AES ALGORITHM

The AES is an iterated piece figure with an altered square size of 128 & a variable key length. The distinctive sorts of

changes work on the middle results, called state. The state is a rectangular cluster of bytes and since the piece size is 128 bits, which is 16 bytes, the rectangular exhibit is of measurements 4x4 cells called lattice. The fundamental unit for preparing in the AES calculation is a byte, which is a grouping of eight bits regarded as a solitary element. The information, yield and Cipher Key bits successions are prepared as varieties of the bytes which are shaped by separating these arrangements into gatherings of eight adjoining bits to frame a varieties of bytes.

In the Rijndael form with the variable piece size, line size is settled to four and the quantity of sections differs. The quantities of sections are the square size isolated by 32 and signified Nb. The figure key is likewise envisioned as a rectangular exhibit with four columns. The quantity of sections of the figure key, indicated Nk, is equivalent to the key length isolated by 32. AES utilizes a variable number of rounds, which are altered: A key of size 128 has 10 rounds.

- AES calculation utilizes a round capacity that is made out of four diverse byte-situated changes, Byte substitution using a substitution table

- Shifting of rows of the State array by using different offsets

- Mixing the data each & every column of the State array

- Adding a Round Key for the State

Above mentioned functions are carried out for each and every individual round and also in the last round the third function which is Mixing the data in each column of the State array will not performed for that the last round is carried out separately. On the basis of key provided, new set of keys will be generated in the Key Expansion block & which is given to the each round as input. Transformations.

# ENCRYPTION

Toward the begin of the Encryption or Cipher, the information and the data key were replicated to the State exhibit utilizing the traditions. At first the XOR operation ought to be performed between every byte of the info information and the data key and the yield will be given as the data of the Round-1. After an underlying Round Key expansion, the State cluster is changed by actualizing a round capacity 10times, with the last round contrasting somewhat from the primary Nr–1rounds. The last State is then replicated to the yield. The round capacity is parameterized utilizing a key timetable that comprises of a one-dimensional exhibit of four-byte words inferred utilizing the Key Expansion schedule.The individual transformations that carried out are as follows-SubBytes, ShiftRows, MixColumns, AddRoundKey

## DECRYPTION

The figure content of 128 bits and the same key of 128 bits will be given as the information to the unscrambling piece. The encoded information will be decoded and the first plain message will be accomplished as the yield of the unscrambling piece. The Cipher changes can be transformed and afterward executed backward request to deliver a clear Inverse Cipher for the AES calculation. The individual changes utilized as a part of the Inverse Cipher were recorded as InvShiftRows, InvSubBytes, InvMixColumns, AddRoundKey

Here likewise 10 rounds will be completed and the main distinction in the unscrambling hinder concerning the calculation stream is that the aftereffect of the KeyExpansion of each round will likewise be given to the MixCoulmns operation after which the AddRoundKey change ought to be conveyed out .InvMixColumns{state XOR Round Key} = InvMixColumns{state} XOR InvMixColumns{Round Key}

The above equation represents the basic difference in the process of the AES Encryption and Decryption algorithm.

## IMPLEMENTATION

The AES is a piece figure. This implies the quantity of bytes that it scrambles is settled. AES can as of now scramble pieces of 16 bytes at once; no other square sizes are in a matter of seconds a part of the AES standard. On the off chance that the bytes being encoded are bigger than the predetermined square then AES is executed simultaneously. This additionally implies AES needs to scramble at least 16 bytes. On the off chance that the plain content is littler than 16 bytes then it must be cushioned. Just said the square is a reference to the bytes that are handled by the calculation.

The present state of the piece will be characterized by the State. That is the square of bytes that are as of now being chipped away at. The state begins off being equivalent to the square, in any case it changes as each round of the calculations executes. Doubtlessly we can say this is the piece in advancement. The Advanced Encryption Standard Algorithm which incorporates both Encryption and Decryption are executed utilizing Verilog and their usefulness will be confirmed in the ModelSim Tool with appropriate experiments.

# IMPLEMENTATION REQUIREMENTS

During the process of implementation, above mentioned different parameters are required to consider.

- Required Input Data Length

- Required Key Length

- Keying Restrictions

- Parameterization of Block Size and Round Number

# .RESULTS AND CONCLUSION

### Design Summary

This describes the simulation on Xilinx navigator summary statement.

| Device Utilization Summary                        |       |           |             |         |  |  |  |

|---------------------------------------------------|-------|-----------|-------------|---------|--|--|--|

| Logic Utilization                                 | Used  | Available | Utilization | Note(s) |  |  |  |

| Number of Slice Flip Flops                        | 551   | 29,504    | 1%          |         |  |  |  |

| Number of 4 input LUTs                            | 2,116 | 29,504    | 7%          |         |  |  |  |

| Logic Distribution                                |       |           |             |         |  |  |  |

| Number of occupied Slices                         | 1,210 | 14,752    | 8%          |         |  |  |  |

| Number of Slices<br>containing only related logic | 1,210 | 1,210     | 100%        |         |  |  |  |

| Number of Slices<br>containing unrelated logic    | 0     | 1,210     | 0%          |         |  |  |  |

| Total Number of 4 input<br>LUTs                   | 2,116 | 29,504    | 7%          |         |  |  |  |

| Number of bonded IOBs                             | 133   | 250       | 53%         |         |  |  |  |

| Number of GCLKs                                   | 1     | 24        | 4%          |         |  |  |  |

| Total equivalent gate count<br>for design         | 17914 |           |             |         |  |  |  |

| Performance Summary    |                     |        |        |  |  |

|------------------------|---------------------|--------|--------|--|--|

| Final Timing           | 0                   | Pinout | Pinout |  |  |

| Score:                 |                     | Data:  | Report |  |  |

| Routing                | All Signals         | Clock  | Clock  |  |  |

| Results:               | Completely Routed   | Data:  | Report |  |  |

| Timing<br>Constraints: | All Constraints Met |        |        |  |  |

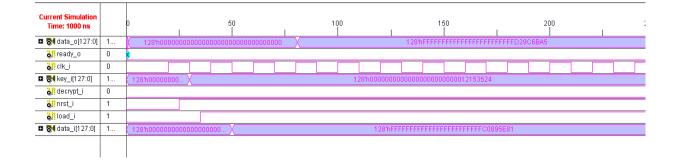

# 5.2 Simulation Waveforms

1) Simulation Waveforms for Initial Round:

### Functional Simulation And Verification

The new improved structure of AES-128 encryption algorithm is implemented with Verilog. We used Xilinx 9.2 ISE for the waveform and verified the results.

## Table 1 Comparison of implementations of AES

| Slices | Through | Throughpu | Suppor | Ref      |

|--------|---------|-----------|--------|----------|

|        | put     | t/Area    | t      |          |

|        | (Gbps)  | (Mb/Sec/S |        |          |

|        |         | lice)     |        |          |

| 1931   | -       | -         | Enc    |          |

|        |         |           |        |          |

| 22994  | -       | -         | Enc/De |          |

|        |         |           | с      |          |

| 8447   | 1.18    | 0.187     | Enc    |          |

|        |         |           |        |          |

| 626    | 3.4     | 5.43      | Enc    |          |

|        |         |           |        |          |

| 1470   | 2.8     | 1.9       | Enc/De |          |

|        |         |           | c      |          |

| 751    | 4.0     | 5.33      | Enc    | Serial   |

|        |         |           |        | Impleme  |

| 953    | 5.26    | 9.21      | Enc/De | Pipeline |

|        |         |           | с      | d        |

|        |         |           |        | Impleme  |

Vol. 5 Issue 04, April-2016

#### CONCLUSION

Productivity as far as engineering improvements, for example, those made in the Advanced Encryption Standard and usage angles prompting Area Optimization & Higher Throughput

In the mean time, this configuration lessens power utilization to some degree, for the force utilization is specifically identified with the chip range.

A usage of region improved AES calculation which meets the genuine application is proposed in this theory. Subsequent to being coded with Verilog Hardware Description Language, the waveform recreation of the new calculation was taken in the Xilinx 9.2 family. Eventually, a union recreation of the new calculation has been finished. The outcome demonstrates that the outline with the pipelining innovation and unique information transmission mode can streamline the chip territory adequately. Then, this outline decreases power utilization to some degree, for the force utilization is specifically identified with the chip region. Along these lines the encryption gadget actualized in this strategy can meet some down to earth applications.

As the S-box is executed by turn upward table in this plan, the chip territory and force can in any case be streamlined. So the future work ought to concentrate on the execution method of S-box.

Science in Galois field (28) can perform the bytes substitution of the AES calculation, which could be another thought of further research.

#### Future Scope

The outcome demonstrates that the outline with the pipelining innovation and exceptional information transmission mode can improve the chip region successfully. Subsequently the encryption gadget actualized in this technique can meet some commonsense Applications like picture encryption.

In this proposal, we have concentrated on AES encryption and unscrambling plots and have highlighted a portion of the vital numerical properties and also the security issues of AES calculation. Since AES gives better security and has less execution intricacy, it has risen as one of the most grounded and most effective calculations in presence today. Subsequently, the ideal arrangement is the utilization of a mixture encryption framework in which commonly AES is utilized to scramble huge information

square. The future work can accomplished for the dissemination of mystery key that is considered as a basic issue of AES like other symmetric encryption calculation.

## REFERENCES

- AI-WEN LUO, QING-MING YI, MIN SHI "Design and Implementation of Area-optimized AES Based on FPGA" Published by 2011 International Conference on Business Management and Electronic Information.

- [2] Kuo-Huang Chang<sup>1</sup>, Yi-Cheng Chen<sup>2</sup>, Chung-Cheng Hsieh<sup>1</sup>, Chi-Wu Huang<sup>2</sup> and Chi-Jeng Chang<sup>1</sup> "Embedded a low area 32-bit AES for image encryption/decryption application" Published by IEEE International Symposium on Circuits and Systems, 2009. ISCAS 2009

- [3] Shanxin Qu; GuochuShou; Yihong Hu; ZhigangGuo; Zongjue Qian "High Throughput, Pipelined Implementation of AES on FPGA" Published in International Symposium on Information Engineering and Electronic Commerce, 2009. IEEC '09.

- [4] Helion Technologies Ltd, "Fast AES XTS/CBC Core for Xilinx FPGA" – (XEX-based Tweaked Codebook with Ciphertext Stealing), IP Core, http://www.heliontech.com/aes\_xex.htm.

- [5] Hatzidimitriou, E.; Kakarountas, A.P.; , "Implementation of a P1619 crypto-core for Shared Storage Media," MELECON 15<sup>th</sup>IEEE Mediterranean Electrotechnical Conference , vol., no., pp.597-601,

- [6] Martin, L.; "XTS: A Mode of AES for Encrypting Hard Disks," Security & Privacy, IEEE, vol.8, no.3, pp.68-69.