# Novel Memory Architecture Dual Dual Core Processor on Altera FPGA DENano Board

Mr. Venkategowda. N<sup>1</sup>, Assistant Professor ECE Dept, MITE, ,Moodbidre.

Mr. Ajay Pinto<sup>2</sup> MITE.

Naveen Pai G<sup>3,</sup> DR.MVSIT

Mr. Shivraj G<sup>4</sup> Student, NMIT, Mangalore,. VTU University Belagum ,Karnataka State, India

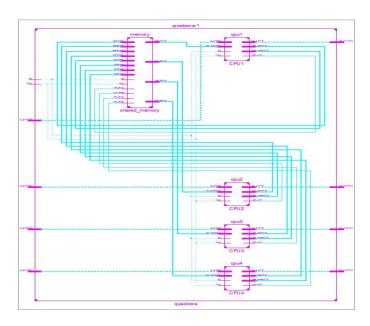

Abstract -This project work presents a framework to design a shared memory and DUAL-Core Processor, on a programmable platform. Complete flow is proposed by a programming model and architecture. The effectiveness of shared memory blocks is demonstrated by implementing on FPGA. The aim of the project is to develop an architecture, design, implement and test DUAL-Core Processor on Altera DE1 FPGA Board. Four Processors are connected in star topology and share common memory for program and data. Depending o the application the Processor is expected to run at 150 MHz, with effective instruction cycle speed of 600MHz (150 x 4).

Index terms - FPGA, programming model, CPU, HW, SW, Dual-core processor, shared memory, RISC instruction set.

## I. INTRODUCTION:

The Multiprocessing represents a new paradigm for processor design. This trend has been pursued most semiconductor industries, both for high performance computer and complex embedded system. Reconfigurable platforms have emerged as an important alternative to the ASIC design, featuring flexibility v/s relatively lower performance. However implementing a multiprocessor on FPGA poses to solve many problems. Most of these issues, such as cache coherence, multiprocessor identification managements, processors synchronization are to be addresses by system designer. This paper presents a platform which simplifies design of shared memory architectured for Dual core processor on FPGA. We introduce a synthesizable architecture and a programming model using verilog which run on commercial FPGA. In the many multiprocessor projects, there has been a heavy focus on either HW or SW to provide facilities for this communication. Both approaches limit speed and flexibility. In the dual-core processors on FPGA give rise to more flexible with high speed and low cost.Importance of multiprocessors has grown throughout in the year 1990s designers sought a way to build servers and supercomputers with higher performance than a single microprocessor.

## II. CONVENTIONAL APPROACH:

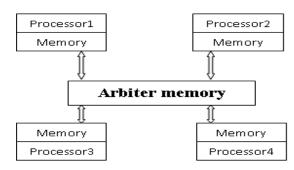

In this approach, the system is designed for parallel execution. The system consists of several processor modules (processor core P1, P2, P3, P4....) and dedicated data memory used for read and writes processor operations by means of memory arbiter.

Figure 1: Conventional approach for dual Core with dedicated memory architecture

If the processor 4 is to communicate with processor 1, it requires more number of clock cycles to transfer the contents in the processor 1 to processor 4 and results in more delay because Processor4 need to place request to arbiter. Arbiter need to approve and send the request to Processor1 is to communicate to arbiter with required data/instruction. Arbiter is to pass on the data/instruction to processor 4

### III. PROPOSED METHOD:

The disadvantages of conventional approach are that if consumes more power, the design utilizes more number of gates, uses four clock cycle and requires one clock per request for each processor, it requires memory arbiter to communicate with all the processor, separate logic circuit as to be designed and for each processor having dedicated memory.

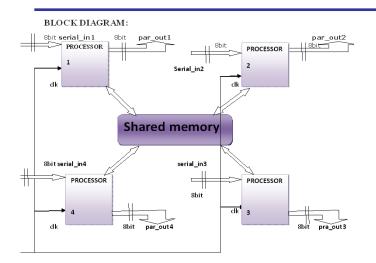

Figure 2: Block Diagram Of Shared Memory Architecture With Dual-Core

Processor

To overcome these disadvantages shared memory architecture for dual core processor is designed with less number of gates. The system consumes less power and latency is also less. Architecture of shared memory dual core processor is shown figure

**Processor-** Non-Pipeline execution, Instruction fetch, Instruction decode, Instruction execution, Register(R/W) **Shared Memory:** DATA input, DATA output ,ADDRESS, READ/write operation. All carried at during same clock. In this approach the shared memory used is called Dual-port memory. Any processor can write/read from the memory at the same time.

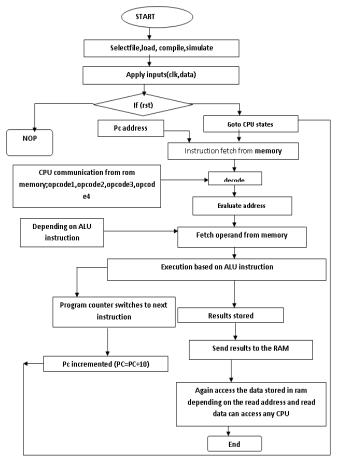

**Methodology:** The steps involved in the dual core processor are as follows:-First designing a processor, designing shared memory, Connecting bus architecture, Simulation, Synthesis and implementation, testing on FPGA board

**Advantages:** In this approach uses only one clock cycle is required to execute a full instruction, Reduced gate count, chip area and power, Decrease in latency and Scalable architecture

#### I. PROCESSOR DESIGN:

Unpipelined implementation is not the most economical or the highest-performance implementation. Instead, it is designed to lead naturally to a pipelined implementation. The number of dependent steps varies with the machine architecture. A non-pipelined processor executes only a single instruction at a time. The specification of processor design as follows:-Architecture contains 23 instructions (6 arthmetic+8 logical+4 datapath+5 branching instruction). Pipelined architecture, Four stage instruction execution (IF, ID, IE, ST), Harvard memory architecture (one for code memory and main memory), 8 bit data and 8bit address bus, 8 bit memory mapped I/O register, 1 Special purpose status registers, 13 General purpose CPU registers. Uniform instruction width for all the instruction.

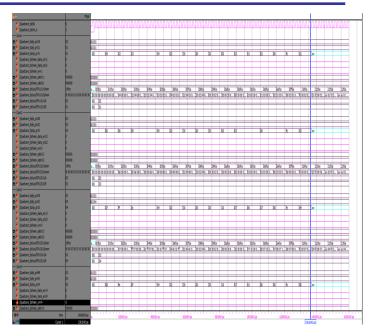

Figure4: Simulation result of CPU performs the ALU operation

Figure5: Flow chart of processor design

#### II. SHARED MEMORY:

Shared-memory machines usually support the caching of both shared and private data. Private data are used by a single processor, while shared data are used by multiple processors; essentially providing communication among the processors through reads and writes of the shared data.

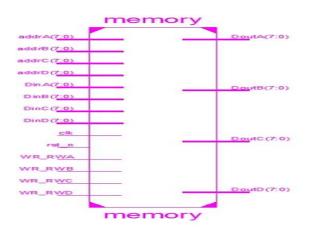

Figure 6: schematic of memory

When a private item is cached, its location is migrated to the cache, reducing the average access time as well as the memory bandwidth required. Since no other processor uses the data, the program behavior is identical to that in a uni processor. Each individual processor are simulated and verified and combined together and designed as Dual core. The respective operation output is shown sequentially in the out bus as shown in the simulation figure.

Figure 7: Shows the flow chart of shared memory.

Figure8:RTL Schematic of memory design

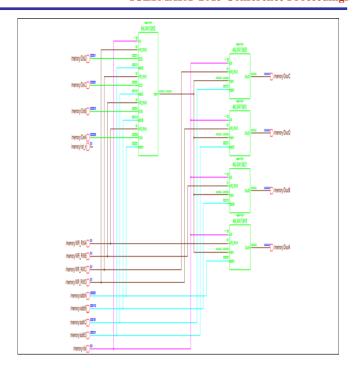

Figure 9: Memory with dual core design

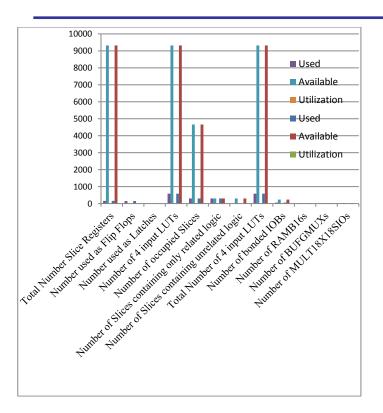

Figure 7: Resource utilization summery

## **CONCLUSION**

In this project we designed a shared memory architecture dual core processor based on FPGA system is designed for this by VERILOG coding adopted by altera model sim 6.6d and xlinx software. Each core is simulated and implemented on hardware and verified for its Arithmetic and Logical Function. The Dual core designed also been implemented on HW and parallel data operation is performed, so that time taken by single processor to perform multiple operation is justified by Dual core, that it takes less time and parallel operation is performed. After synthesis we got the less no of logic resource utilization comparing the available resources.

## REFERENCES

- International Transactions on Multi-Core Systems, Vol. 19, No. 5, May 2011.Hardware Synchronization for Embedded Multi-Core Processors on FPGA

- [2] Design and Implementation of a 32bit RISC Processor on Xilinx FPGA, Wael M ElMedany<sup>1</sup>, Khalid A AlKooheji, <sup>1</sup> Department of Communications and Electrical Engineering, Faculty of Engineering, Fayoum University, Egypt, Computer Engineering Department, Information Technology College, University Of Bahrain, 32038 Bahrain.

- [3] The Design of a RISC Architecture and its Implementation with an FPGA Niklaus Wirth, 11.11.2011 and Xilinx, Spartan-3 Starter kit board user guide.

- [4] White paper NVIDIA benefits of Dual Core CPUs in Mobile Devices. Copyright © 2011 NVIDIA Corporation. All rights reserved.

- [6] International Scientific Conference Computer Science'2008, Shared Memory Design for Multi core Systems, Peter Manoilov, Plamena Krivoshieva Technical University, Sofia, Bulgaria.

- [7] Kamburov G., P.Manoilov, P. Zaykov, P. Borovska, "Parallel Architecture Implemented in FPGA Based on Shared Memory System", Third International Scientific Conference COMPUTER SCIENCE, 2006, Conference Proceedings, pp.96-101, Instanbul, Turkey.

- [8] Lazarova M., "Hough Transform for Line Detection in Images on Shared Memory Multiprocessor Platform", Proc. of International Conference on Automatics and Informatics, Sofia, Bulgaria, October 3 - 6, 2007.

- [9] Vincent P.Heuring, and Harry F.Jordan, "Computer Systems Design and Architecture", 2nd Edition, 2008.

[10] Samuel O. Aletan,"An Overview of RISC Architecture", Proc.

- [10] Samuel O. Aletan,"An Overview of RISC Architecture", Proc. Symposium on Applied Computing, 1992, pp.11-12. [2] Design and Implementation of a 64-bit RISC Processor using VHDL, 2009 IEEE.

- [11] Brunelli Claudio, Cinelli Federico, Rossi Davide, Nurmi Jari, "A VHDL model And implementation of a coarse grain reconfigurable coprocessor for a RISC core", 2nd Conference on Ph.D. Research in Microelectronics and Electronics Proceedings, PRIME, 2006, p 229232.

- [12] Rainer Ohlendorf, Thomas Wild, Michael Meitinger, Holm Rauchfuss, Andreas Herkersdorf, "Simulated and measured performance evaluation of RISC based SoC Platforms in network processing applications", Journal of Systems Architecture 53 (2007) 703–718.

- [13] "Some facts about the Acorn RISC Machine" Roger Wilson posting to comp.arch, 2 November 1988. Retrieved 25 May 2007.

- [14] "MCU Market on Migration Path to 32-bit and ARM-based Devices: 32-bit tops in sales; 16-bit leads in unit shipments". IC Insights. 25 April 2013. Retrieved 1 July 2014.

- [16] Grabham, Dan (19 July 2013). "From a small Acorn to 37 billion chips: ARM's ascent to tech superpower". TechRadar. Retrieved 8 November 2013.

- [17] McGrath, Dylan (18 July 2011). "IHS: ARM ICs to be in 23% of laptops in 2015". EE Times. Retrieved 20 July 2011.

- [18] "ARM Launches Cortex-A50 Series, the World's Most Energy-Efficient 64-bit Processors" (Press release). ARM Holdings. Retrieved 31 October 2012.

- [19] Parrish, Kevin (14 July 2011). "One Million ARM Cores Linked to Simulate Brain". EE Times. Retrieved 2 August 2011.

## **AUTHORS PROFILE:**

Mr. Venkategowda N received his Bachelor of engineering degree in Medical Electronics from visveswaraya Technical University, belagaum, Karnataka, India in 2010 and Post Graduate degree in VLSI Design and Embedded system from VTU University, Karnataka, India in 2012. He started his carrier as Assistant Professor in AIT tumkur and sampoorna institute of technology and research VTU. Currently working as Assistant Professor in mangalore institute of technology and engineering, mangalore, karnataka INDIA. His research interests include vlsi, embedded system, Imageprocessing and medical electronics.

Mr.Basavaraj H.J received his Bachelor of engineering degree in Electronics and instrumentation from kuvempu University, belagaum, Karnataka, India in 2007 and Post Graduate degree in digital signal processing from VTU University, Karnataka, India in 2012. He started his carrier as Assistant Professor in MITE mangalore. Currently working as Assistant Professor in mangalore institute of technology and engineering, mangalore, karnataka INDIA.

**Mr.AjayPinto** received his Bachelor of engineering degree in Electronics and communication from visveswaraya Technical University, belagaum, Karnataka, India in 2010 and Post

Graduate degree in digital electronics and communication system from VTU, Karnataka, India in 2012He started his carrier as Assistant Professor in SSE Mukka, mangalore. Currently working as Assistant Professor in mangalore institute of technology and engineering, mangalore, karnataka INDIA. His research interests include electronics and communication system and power systems

Mr.naveen pai received his Bachelor of engineering degree in Electronics and communication from visveswaraya Technical University, belagaum, Karnataka, India in 2009 and Post Graduate degree in digital electronics and communication system from VTU, Karnataka, India in 2013.He started his carrier as Assistant Professor in Dr MVSIT, mangalore. INDIA. His research interests include electronicsand communication system and power systems and vlsi