# Low Leakage Cell for Ternary Content Addressable Memory: A Tutorial and Review

Ankaj Gupta<sup>1</sup>

Department of Electronics& Communication Engineering,

Ganga Institute of Technology and Management,

Kablana, Jhajjar, Haryana, India

Abstract- Ternary Content addressable Memory (TCAM) has been an emerging technology for packet forwarding in Network Router. New architecture innovations are reducing power and leakage in TCAM. Beside power, leakages also constitute a major part in TCAM performance. In this paper we review various schemes for low leakage TCAM. The circuits have been implemented in 0.35- $\mu$ m CMOS technology. The minimum power supply is 1.5 V and the maximum supply current is 11.5  $\mu$ A for a temperature range of 25°C to 30°C.

Index Terms- TCAM Cell, Leakage Current, Power Dissipation

#### I. INTRODUCTION

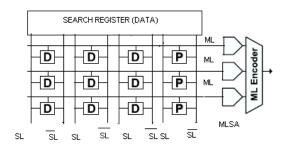

A Content Addressable Memory (CAM) is an outgrowth of random access memory (RAM) technology. Unlike RAMs which access a word based on its address, CAMs access a word based on its contents. A CAM compares an incoming key with all the words in parallel and returns the address of the best match in the array [1]. Therefore CAM is an application specific memory that allows its entire contents to be searched within a single clock cycle. TCAM applications include parametric curve extraction [2], transformation [3], Huffman coding/decoding [4], [5], Lempel–Ziv compression [6]-[9], and image coding [10]. Techniques are described to reduce leakage. Fig.1 gives general view of TCAM architecture. The input to the system is the search word that is broadcast onto the search lines to the table of stored data. Each stored word has a matchline that indicates whether the search word and stored word are

Fig. 1. Schematic of TCAM

identical (the match or are different (a mismatch case, or miss).

#### II. TCAM CELL

## 1.1 Leakage Current Component

The leakage current of a deep sub micrometer CMOS transistor consists of three major components: junction tunneling current, subthreshold current and tunneling gate current [11]. In this section, each of these three components is briefly described

**1.1.1**Subthreshold Leakage Current: Subthreshold leakage is the drain-source current of a transistor when the gate-source voltage is lower than the threshold voltage. The subthreshold leakage is modeled as [11].

$$I_{sub} = A_{sub} \exp\left(\frac{q}{n'kT}(V_{GS} - V_{to} - \lambda'V_{SB} + \eta)\right)$$

$$V_{DS}) \times \left(1 - \exp(-\frac{q}{kT}V_{DS})\right)$$

(1)

Where

$C_{OX}$  = Gate oxide capacitance per unit area

W = Width of the Transistor

L = Effective Length of the transistor

K = Boltzman's Constant

T = Absolute Temperature

$\lambda'$  = Linearized body effect cofficient

$\eta$  = Drain induced barrier Lowering (DIBL)

$\eta'$  = Subthreshold Swing coefficient of the transistor

1.1.2 Tunneling Gate Leakage Current: Electron tunneling from the conduction band, which is only significant in the accumulation region, results in direct tunneling gate leakage current in nMOS transistors. In pMOS transistors, hole tunneling from the valence band results in the tunneling gate leakage current. If is used for the gate oxide, pMOS transistors will have about one order of magnitude smaller gate leakage than nMOS transistors Therefore, one may conclude that the major source of tunneling gate leakage in CMOS circuits is the gate-to channel tunneling current of the ON nMOS transistors which can be modeled as [12]

$$J_{tunnel} = \frac{4\pi m * q}{h^3} (kT) 2 \left( 1 + \frac{\gamma kT}{2\sqrt{E_B}} \right) \times \exp\left( \frac{E_F}{KT} - \gamma \sqrt{E_B} \right)$$

Where  $m*(=0.19M_o) = Electron transfer mass$

$M_o$  = Electron Rest Mass

h= plank's Constant

$E_F = Fermi Level at the Si/SiO_2 interface$

$E_B$  = Height of Barrier

$$\gamma = \frac{4\pi Tox \sqrt{2m_{ox}}}{h} \tag{3}$$

Where  $m_{ox}$  (= 0.32 $M_o$ ) = Effective Electron Mass in the Oxide

The major contributor to the tunneling gate leakage current in a 6T SRAM cell is the gate-to-channel leakage of the ON pull-down transistor. To weaken this leakage path, one needs to increase the gate-oxide thickness of the pull-down transistors. To reduce other (minor) tunneling gate leakage currents in the SRAM cell, one only needs to increase the gate oxide thickness of the pass transistors, because from the previous discussion, it can be concluded that the gate leakage saving achieved by increasing the oxide thickness of the pMOS transistors would be quite small. Increasing the oxide thickness of a transistor not only increases the threshold voltage, but also reduces the drive current of the transistor. So, the effect of applying this technique to an SRAM cell is an increase in the read/write delay of the cell. This is general equation for leakage in SRAM cell that govern all leakage in TCAM memory.

### 1.2 Conventional Cell16T TCAM

Fig. 2. shows the leakage paths in a 6T-SRAM-based TCAM cell when the BLs are charged to the 'mask' state (BL1 = BL2 = '0'), and minimum-size transistors are used. I<sub>SN</sub> and I<sub>SP</sub> are NMOS and PMOS subthreshold leakages respectively. NMOS gate leakages are specified by I<sub>GON</sub> and IGOFF for 'ON' and 'OFF' transistors, respectively. Similarly I<sub>GONP</sub> and I<sub>GOFFP</sub> are PMOS gate leakages.

| Leakage<br>Current    | Measured<br>Current                    | Modified Value (fA) |

|-----------------------|----------------------------------------|---------------------|

| 2I <sub>SN</sub>      | 2(-4.9087 n+<br>802.77f)               | -9.815 e6 f         |

| 2I <sub>SP</sub>      | 2(6.0318 u + 3.6117 u)                 | 19.287 e9 f         |

| 2I <sub>GON</sub>     | 2(-1.8082 f +<br>4.998 e-16 A)         | -2.6168 f           |

| 6I <sub>GOFF</sub>    | 6(1.3378 e-17<br>A+ -2.934 e -<br>17A) | -9.5772 e-2 f       |

| 2I <sub>GONP</sub>    | 2(3.20 f + -1.089<br>e -16 A)          | 6.1822 f            |

| 2I <sub>GOFFP</sub> K | 2(-9.2001 e-16A<br>+ 3.6729 e-16A)     | -5.5272 e-1 f       |

Assuming random data, a TCAM column with shared BLs has the same probability of storing '0', '1' and 'mask' states. Hence, one-third of the bits will be masked and setting the BLs to the 'mask' state minimizes the subthreshold leakage. For example, if the BLs are set to '0' (BL1 = '0', BL2 = '1'), the subthreshold leakage through the access transistors will be 2I<sub>SN</sub> when the stored value is 'mask'. Typically, the driver transistors (NMOS in the cross-coupled inverters) are sized nearly 2 to 2.5 times larger than the access transistors to perform fast READ operation without disturbing the stored data.

$$\begin{split} &I_{6T\_Mask}/_{BLs} = Mask = 2I_{SN} + 2I_{SP} + 2I_{GON} + 6I_{GOFF} + 2I_{GONP} \\ &+ 2I_{GOFFPK} \end{split} \tag{4}$$

Larger transistors result in greater leakages. Since the READ speed is not critical in a TCAM, minimum size transistors can be USED.

This choice also reduces the cell area. Conventional SRAMs also precharge BLs to VDD in order to perform fast READ operation.

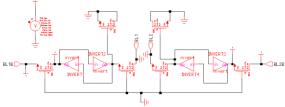

Fig. 2. Conventional TCAM Cell

| Leakage<br>Current    | Measured<br>Current                    | Modified Value (fA) |

|-----------------------|----------------------------------------|---------------------|

| 2I <sub>SN</sub>      | 2(-4.9087 n+<br>802.77f)               | -9.815 e6 f         |

| 2I <sub>SP</sub>      | 2(6.0318 u + 3.6117 u)                 | 19.287 e9 f         |

| 2I <sub>GON</sub>     | 2(-1.8082 f + 4.998 e-16 A)            | -2.6168 f           |

| 6I <sub>GOFF</sub>    | 6(1.3378 e-17<br>A+ -2.934 e -<br>17A) | -9.5772 e-2 f       |

| 2I <sub>GONP</sub>    | 2(3.20 f + -1.089<br>e -16 A)          | 6.1822 f            |

| 2I <sub>GOFFP</sub> K | 2(-9.2001 e-16A<br>+ 3.6729 e-16A)     | -5.5272 e-1 f       |

TABLE I

LEAKAGE CURRENT OF CONVENTIONALJ TCAM

Table I gives leakage current of different transistor of 16 T TCAM Cell. In TCAMs, BLs can be precharged to the state, which results in the minimum leakage. Figure 1 can be used to calculate the leakage current for a 6T-SRAM-based TCAM cell as given by equation (3) for different storage conditions. Below table abbreviations

## 1.3 NMOS-Coupled TCAM Cell

Till this point we have studied conventional TCAM cell. In 2006, Nitin and Manoj [13] presented a novel ternary storage cell. In this paper we have review this NMOS and

Next PMOS technique .Each TCAM cell contains two SRAM cells to store the ternary value. These SRAM cells can have four combinations: '00', '01', '10', and '11'. Table II shows leakage current of NMOS coupled TCAM cell

| Leakage<br>Current | Measured<br>Current                | Modified Value (fA) |

|--------------------|------------------------------------|---------------------|

| 2I <sub>SN</sub>   | 2(-4.9087 n+<br>802.77f)           | -9.815 e6 f         |

| 2I <sub>SP</sub>   | 2(6.0318 u + 3.6117 u)             | 19.287 e9 f         |

| 2I <sub>GON</sub>  | 2(-1.8082 f + 4.998 e-16 A)        | -2.6168 f           |

| <b>6I</b> GOFF     | 6(1.3378 e-17 A+<br>-2.934 e -17A) | -9.5772 e-2 f       |

| 2I <sub>GONP</sub> | 2(3.20 f + -1.089<br>e -16 A)      | 6.1822 f            |

| 2IGOFFPK           | 2(-9.2001 e-16A<br>+ 3.6729 e-16A) | -5.5272 e-1 f       |

TABLE II

LEAKAGE AT NMOS COUPLED TCAM

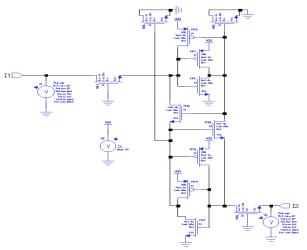

. However, only three out of them are used for the ternary value, and the "unused" state (typically '11') is forbidden. This ternary storage cell trades this "unused" state for a smaller leakage by coupling two 5T-SRAM cells and eliminating a subthreshold leakage path [13]. Fig. 3 shows the leakage paths of the NMOS-coupled (NC) ternary storage cell that connects two 5T-SRAM cells . For storing a ternary '0' or '1', one of the storage nodes (connected to the access transistors) is held at logic '0'through the coupling NMOS transistor. Likely when the 'mask' state is stored, both coupling NMOS transistors are 'OFF'. Note that when both coupling NMOS transistors are 'ON', the cell is not stable. Hence, this cell can store only three states. It can be noticed in Figure 3. that the proposed cell can store only three states because the coupling does not allow the "unused" state. The total leakage current for an NC-TCAM cell (with BLs = 'mask') can be given by equation

$I_{NC\_MASK/BLs=Mask} = 2I_{SN} + 2I_{SP} + 2I_{GON} + 6I_{GOFF} + 2I_{GONP} + 2I_{GOFFP}$  (6)

Thus, it will exhibit less leakage than the 5TSRAM- based cell only if condition (7) is satisfied:

$$0.67I_{SN} > 3.33I_{GOF F} \rightarrow I_{SN} > 5I_{GOFF}$$

(7)

Fig. 3. NMOS Coupled TCAM Cell

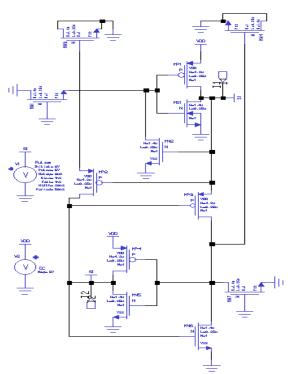

## 1.4\_P-MOS Coupled TCAM Cell

The coupling between the two 5T-SRAM cells can also be obtained by PMOS transistors. Fig. 4. shows the leakage paths of the PMOS-coupled (PC) TCAM cell. Similar to the NC-TCAM cell, one of the coupling PMOS transistors does not consume subthreshold leakage under '0' and '1' conditions. Thus, it will also exhibit smaller leakage than the 5T-SRAM-based cell if the subthreshold leakage is more than the gate leakage. The total leakage current for a PC-TCAM cell (with BLs set to the 'mask' condition) can be given by equation (6).

$$I_{PC\_MASK/BLs=Mask} = 2I_{SN} + 2I_{SP} + 2I_{GON} + 2I_{GOFF} + 2I_{GONP} + 2I_{GOFFP}$$

(8)

Similar to the 5T-SRAM-based cell, this BL precharge condition reduces both subthreshold and gate leakages. The PC-TCAM cell will consume less leakage than the 6T-SRAM-based cell only if condition (9) is satisfied.

$$0.67 I_{SP} > 0.67 I_{GOFFP} \rightarrow I_{SP} > I_{GOFFP}$$

(9)

Similarly, the PC-TCAM cell will consume less leakage than the NC-TCAM cell (when BLs = 'mask') only if condition (10) is satisfied.

$$0.67$$

lsp +  $3.33$ lgoff >  $0.67$ lsn +  $0.67$ lgoffp  $\rightarrow$  lsp +  $5$ lgoff > lsn + lgoffp (10)

Table III gives leakage current of PMOS coupled TCAM cell

| Leakage               | Measured                               | Modified Value |  |  |

|-----------------------|----------------------------------------|----------------|--|--|

| Current               | Current                                | (fA)           |  |  |

| 2I <sub>SN</sub>      | 2(0 + 91.328 n)                        | 182.64 e6 f    |  |  |

| 2I <sub>SP</sub>      | 2(-526.3173 f + -9.481 e-18 A)         | -1.052 e-3 f   |  |  |

| 2I <sub>GON</sub>     | 2(0 + 2.20803<br>e-17A)                | 4.41606 e-2 f  |  |  |

| 2I <sub>GOFF</sub>    | 2(0 + 1.4698 e-<br>18A)                | 2.9392 e-3 f   |  |  |

| 2I <sub>GONP</sub>    | 2(0 + -2.4130<br>e-18A)                | 4.82 e-3 f     |  |  |

| 2I <sub>GOFFP</sub> K | 2(-5.9084 e-17<br>A + 5.1861 e-<br>17A | -14.4 e-3 f    |  |  |

TABLE III LEAKAGE AT PMOS COUPLED TCAM

If the gate leakage is comparable to the subthreshold leakage (ISN < 3IGOFF) and BLs of NCTCAM are at GND, the PC-TCAM cell will consume less leakage than the NC-TCAM cell if condition (10) is satisfied.

$$0.67_{ISP} + 1.33I_{GOFF} > 0.67I_{GOFFP} \rightarrow I_{SP} + 2I_{GOFF} > I_{GOFFP}$$

Most CMOS processes will satisfy condition (8) because the PMOS subthreshold leakage and the NMOS gate leakage both are typically larger than the PMOS gate leakage.

The leakages of the above cells (when BLs = 'mask') are summarized in Table IV. It can be shown that that the 6T-SRAM-based cell always consumes more leakage than the other three cells

Fig . 4. PMOS Coupled TCAM Cell

| Cell | Stored<br>Value | Subthreshold<br>Leakage             | NMOS<br>Gate<br>Leakage                | PMOS<br>Gate<br>Leakage                    |

|------|-----------------|-------------------------------------|----------------------------------------|--------------------------------------------|

| 6T   | ×               | 2I <sub>SN</sub> + 2I <sub>SP</sub> | 2I <sub>GON</sub> + 6I <sub>GOFF</sub> | 2I <sub>GONP</sub><br>+2I <sub>GOFFP</sub> |

| PC   | ×               | 2I <sub>SN</sub> + 2I <sub>SP</sub> | 2I <sub>GON</sub> + 2I <sub>GOFF</sub> | 2I <sub>GONP</sub><br>+2I <sub>GOFFP</sub> |

| NC   | ×               | 2I <sub>SN</sub> + 2I <sub>SP</sub> | 2I <sub>GON</sub> + 6I <sub>GOFF</sub> | 2I <sub>GONP</sub><br>+2I <sub>GOFFP</sub> |

TABLE IV LEAKAGE CURRENT OF TCAM WHEN BITLINE=MASK

## III SIMULATION RESULT

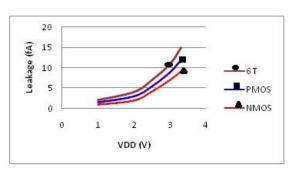

We simulated the above TCAM cells using 0.35 µm technology. Figure 5 shows the leakage of different TCAM cells at 0.35µm CMOS technologies. It can be noticed that the magnitudes of different leakage components are related as follows:

## ISN > ISP >> IGON > IGOFF >> IGONP > IGOFFP

Fig. 5. TCAM Cell Leakage for 35 nm CMOS technology

In this writing 1 was more difficult than writing 0 as it is tough to transfer 1 from NMOS transistor. The conventional 16 transistor TCAM area consume most area and hence most power dissipation. Newer approach like NMOS and PMOS use less area as number of transistor is less as well less power dissipation.

#### IV CONCLUSION

In this work we have studied and analyzed TCAM circuits with an emphasis on high capacity RAM. We have simulated conventional 16 transistor TCAM cell, NMOS coupled TCAM cell and PMOS coupled TCAM cell for low leakage and less area. Simulation results shows a reduction of up to 38% leakage reduction in NMOS and PMOS coupled TCAM cell as compared to conventional TCAM cell. The efficiency of PMOS coupled TCAM cell is best in all category

#### ACKNOWLEDGMENT

This work has been performed on Mentor-Graphics Tools at VLSI Design Lab, Department of Electronics and Communication Engineering, Guru Jambheswar University of Science and Technology, Hisar-125001

#### REFERENCES

- [1] T. Kohonen, *Content-Addressable Memories*, 2nd ed. New York: Springer-Verlag, 1987.

- [2] M. Meribout, T. Ogura, and M. Nakanishi, "On using the CAM concept for parametric curve extraction," *IEEE Trans. Image Process.*, vol. 9, no. 12, pp. 2126–2130, Dec. 2000.

- [3] M. Nakanishi and T. Ogura, "Real-time CAM-based Hough transform and its performance evaluation," *Machine Vision Appl.*, vol. 12, no. 2, pp. 59–68, Aug. 2000.

- [4] E. Komoto, T. Homma, and T Nakamura, "A high-speed and compactsize JPEG Huffman decoder using CAM," in *Symp. VLSI Circuits Dig. Tech. Papers*, pp. 37–38,1993.

- [5] L.-Y. Liu, J.-F.Wang, R.-J.Wang, and J.-Y. Lee, "CAM-based VLSI architectures for dynamic Huffman coding," *IEEE Trans. Consumer Electron.*, vol. 40, no. 3, pp. 282–289, Aug. 1994.

- [6] B. W. Wei, R. Tarver, J.-S. Kim, and K. Ng, "A single chip Lempel-Ziv data compressor," in *Proc. IEEE Int. Symp. Circuits Syst.* (ISCAS), vol. 3, pp. 1953–1955, 1993.

- [7] R.-Y. Yang and C.-Y. Lee, "High-throughput data compressor designs using content addressable memory," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, vol. 4, pp. 147–150, 1994..

- [8] C.-Y. Lee and R.-Y. Yang, "High-throughput data compressor designs using content addressable memory," *IEE Proc.—Circuits, Devices and Syst.*, vol. 142, no. 1, pp. 69–73, Feb. 1995.

- [9] D. J. Craft, "A fast hardware data compression algorithm and some algorithmic extansions," *IBM J. Res. Devel.*, vol. 42, no. 6, pp. 733– 745, Nov. 1998.

- [10] S. Panchanathan and M. Goldberg, "A content-addressable memory architecture for image coding using vector quantization," *IEEE Trans. Signal Process.*, vol. 39, no. 9, pp. 2066–2078, Sep. 1991.

- [11] B. Amelifard, F. Fallah, and M. Pedram, "Low-leakage SRAM design with dual Vt transistors," in *Proc. Int. Symp. Quality Electron. Dec.*, pp. 729–734, 2006.

- [12] F. Hamzaoglu, Y. Te, A. Keshavarzi, and K. Zhang, "Dual V-SRAM cells with full-swing single-ended bit line sensing for high-performance on-chip cache in 0.13 \_m technology generation," in *Proc. Int. Symp. Low Power Electron. Des.*, pp. 15–19, 2006.

- [13] N. Mohan, and M. Sachdev, "Novel ternary storage cells and techniques for leakage reduction in ternary CAM, "Proceedings of the IEEE Iinternational SOC conference (SOCC), Austin, Texas, Sep. 24-27, 2006.