# LDPC Codes for Error Free Transmission of Image over an AWGN Channel

Naveenkumar M Hanchinamani, Amaregouda, Karthik.B.S, Jayanth.C

Telecommunication Engineering Department Dayananda Sagar College of Engineering

# 1. INTRODUCTION

**ABSTRACT** - The error-correcting performances of low-density parity check (LDPC) codes are used here for error free transmission of image for a long distance. The image/photo is well transformed and the coding schemes are applied. We can send not only the image also videos and any Data (huge data). So here when LDPC decoded using practical iterative decoding algorithms, is known to be close to Shannon limits. In this paper we study the LDPC codes performance when varying code rate, constellation level and the maximum number of iteration, when large data stream is applied as image. This paper shows better coding gain can be obtained at the cost of higher complexity or higher bit rate. For some cases, due to their inability to reach very low bit error rates (e.g., 10-12) at low signal-to-noise ratios (SNRs), a consequence the error rate floor phenomenon associated with iterative LDPC decoders is produced. This paper demonstrates that the concatenation system used LDPC as an inner code and the Bose, Chaudhuri, and Hocquenghem codes (BCH) as an outer code can successfully to lower the floor of image data. Connecting BCH codes lower the LDPC BER floor by a factor (from 32 to 22) at about SNR (from -1dB to 1.8 dB) with the same overall code rate (i.e. without any reduction in the bandwidth efficiency) and restricted few number of iteration (only 5 iterations) in an AWGN channel used.

**KEYWORDS**: Image, Data, LDPC, BCH, AWGN.

This became widely recognized that a full utilization of the available bandwidth cannot be achieved without powerful error-control schemes for huge data as of image. LDPC codes are type of interest channel coding techniques in obtaining rates close to the Shannon channel capacity, besides LDPC codes have an easily parallelizable decoding algorithm which consists of simple operations such as addition, comparison and table look-up. Moreover the degree of parallelism is "adjustable "which makes it easy to trade-off throughput and complexity. LDPC codes were discovered by Gallager in 1962, but they were not given much attention for decades as the technology at the time was not mature for efficient implementation. In 1981, Tanner introduced a bipartite graphical representation of low-density parity-check matrices known as the Tanner graph. The use of Tanner graphs as a graphical interpretation of LDPC codes lead researchers to consider the use of existing iterative message-passing algorithms to decode LDPC codes, thus resulting in the rediscovery of LDPC codes. In this paper we are giving much concentration on reducing errors of image data using LDPC codes rather than that of image theory.

# **ORGANIZATION OF PAPER**

Section 1 gives the brief introduction of the system, the block diagram of the LDPC Codes for Error Free Transmission of Image over an AWGN Channel is explained in section 2, section 3 gives the details of the different coding schemes used and implementation, and the simulation results are explained in section 4 and followed by the future scope in section 5.

## 2. BLOCK DIAGRAM OF LDPC CODES

### LDPC Binary Image Modulator Encoder Encoder input Data AWGN Channel Demodulat BCH LDPC Image Binary Output or Data Decoder Decoder

Figure (1) Block diagram of LDPC Codes for Error Free Transmission of Image over an AWGN Channel

The proposed system model (Figure (1)) has the LDPC code used as the inner Code and BCH as the outer code. A message (x) which has been converted from input image to binary for an [n, k] BCH code must be a k-column binary Galois array. The code (y) that corresponds to that message is an n-column binary Galois array. Each row of these Galois arrays represents one word. The codeword generated by the BCH encoder is then recoded by using LDPC encoder to produce a new codeword (z). After the coded bit sequence has been obtained, it is applied to different level of Phase Shift Key (M-PSK) modulator or any modulation techniques (QPSK, BPSK Etc.....). This modulated waveform(c) is transmitted over AWGN channel, where the noise is assumed to be additive white Gaussian noise with zero mean and variance  $\sigma^2$ . Finally, the errors in the received signal (c<sup>\(\delta\)</sup>) are detected and corrected when passing through the demodulator and the decoders (i.e. z^, y^). The simulation results is divided into three sections the first one dealing with conversion of image to binary (later it again converted back to image). In the second, evaluation of Low Density Parity Check code (LDPC) performance when varying the parameters related to its frame work. The third section focus on improving the LDPC performance by concatenated it with Bose, Chaudhuri, and Hocquenghem codes (BCH code).

# 3. CODES

# 3.1 BCH codes

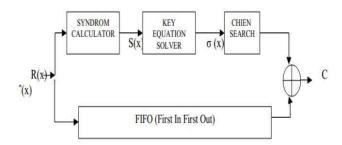

An (N, K, t) BCH code has a block length of N bits and information length of K bits. While Operating under GF (2m), it has the error-correcting capability t, where  $N-K \le m \times t$ ., the conventional BCH decoding contains three major steps. The received polynomial R(x) is loaded into the First in First out (FIFO) and fed into the syndrome calculator to generate syndrome polynomial. As shown in fig (2).

Figure (2) Parity-check matrix in approximate lower triangular form

$$S(x) = S_1 + S_2 x^1 \pm - - - \mp S_{2t} x^{(2t-1)}$$

This is expressed as:

$$S_{j} = R(\alpha^{j}) = \sum_{i=1}^{v} (\alpha^{j})^{ei} =$$

$$\sum_{i=1}^{v} (\beta_{ei})^{j} \qquad for j = 1 \sim 2$$

Where  $\alpha$  is the primitive element over GF (2m) and v is the number of actual errors. Notice that ei is the ith actual error location and  $\beta ei$  indicates the corresponding error locator. The key equation solver is used to carry out the error location polynomial  $\sigma(x)$ , which is defined as:[16]

$$\sigma(x) = (1 + x\beta_{e1})(1 + x\beta_{e2}) \dots \dots (1 + \beta_{ev})$$

= 1 + \sigma\_1 x^1 + \sigma\_2 x^2 \dots \dots + \sigma\_v x^v

The key equation describing the relation between S(x) and  $\sigma(x)$  is derived as:

$$\Omega(x) = S(x) * \sigma(x) \bmod x^{2t}$$

Where  $\Omega(x)$  is the error evaluator polynomial. The most popular methods for solving the key equation are Berlekamp–Massey and modified Euclidean algorithms. After the key equation solver, Chien search is applied to find the roots of  $\sigma(x)$ . If an error is occurred at the  $e_i$ th position,  $\sigma^{-ei}$  will be a root of  $\sigma(x)$ . Finally, the estimated codeword polynomial is obtained by outputting R(x) from the FIFO and inversing those values at error locations.

### 3.2 LDPC codes

LDPC codes can be described by a sparse parity-check matrix H containing a sparse number of non-zero entries. The term low-density means that the number of ones in each column and row of the parity-check matrix is small compared to the block size. Linear codes are defined in terms of generator and parity-check matrices.

Generator matrix G maps information u to transmitted blocks x called codeword. For a generator matrix G, there is a parity-check matrix H which is related as G.  $H^T = 0$ . All codewords must satisfy x.  $H^T = 0$  in terms of the parity-check matrix H. If the parity-check matrix H has the same weight per row and the same weight per column, the resulting LDPC codes is called regular. We use a two tuple (dv, dc) to represent a regular LDPC code whose column weight is dv and row weight is dc. When the weight in every column is not the same in the parity-check matrix, the code is known as an irregular LDPC code.

Low-Density Parity-Check (LDPC) codes are linear error control codes with:

- Sparse parity-check matrices

- Long block lengths that can attain performance near the Shannon limit.

# 3.2.1 LDPC representation

Generally there are two different methods to represent LDPC codes. Like all linear

block codes they can be described via matrices. The second method is a graphical representation.

# **Matrix representation**

The matrix defined in figure (3) is a parity check matrix with dimension  $n \times m$  for a (8, 4) code. We can now define two numbers describing these matrixes. Wr for the number of 1's in each row and wc for the columns. For a matrix to be called low-density the two conditions wc << n and wr << m must be satisfied.

$$H = \begin{bmatrix} 0 & 1 & 0 & 1 & 1 & 0 & 0 & 1 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \end{bmatrix}$$

Figure (3) Matrix representation

# Tanner graph representation

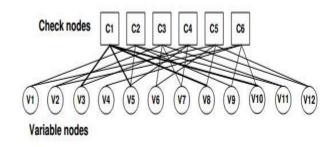

The two types of nodes in a Tanner graph are called variable nodes (v-nodes) and check nodes (c-nodes). Figure (4) is an example for such a Tanner graph and represents the same code as the matrix in figure (3). The creation of such a graph is rather straight forward. It consists of *m* check nodes (the number of parity bits) and *n* variable nodes (the number of bits in a codeword). Check node *fi* is connected to variable node *cj* if the element *hij* of H is a 1.

Figure (4) Tanner graph representation

# **Implementation**

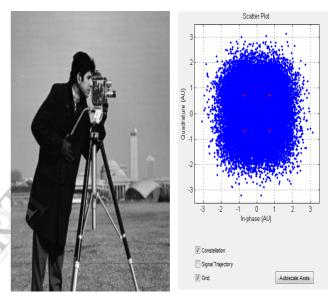

This work is carried out and implemented using MATLab. In this first we have to convert image to binary data stream and then fed it into the BCH and LDPC blocks and it will undergone into modulation. We can use any modulation technique (BPSK, QPSK). Here we are used QPSK as for example and tested it for other algorithms also. The modulated signal is transmitted over an AWGN channel where the occurrence of noise and added errors will takes place.

The reverse operation is takes place at the receiver end. Finally the transmitted image is reconstructed successfully.

### 4. SIMULATION AND RESULT

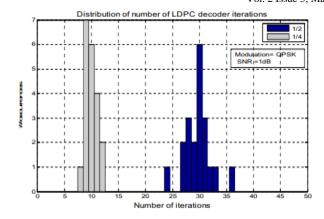

The simulation results is divided into three sections the first one dealing with the image processing. Second is evaluation of Low Density Parity Check code (LDPC) performance when varying the parameters related to its frame work. The second section focus on improving the LDPC performance by concatenated it Bose, Chaudhuri, and Hocquenghem codes (BCH code). So the simulation results are shown in figure (6). The table (1) gives the SNR for modulation schemes various tested Distribution of number of LDPC decoder iterations for different code rate for an image in figure (5).

| Modulation | Effective | SNR required to achieve BER of 10 <sup>-4</sup> |                  |

|------------|-----------|-------------------------------------------------|------------------|

|            | SNR       | No of                                           | No of iterations |

|            |           | iterations                                      | reduced to 10    |

|            |           | reduced                                         |                  |

|            |           | to 20                                           |                  |

| QPSK       | 1Db       | 1.2dB                                           | 2dB              |

| 8PSK       | 4Db       | 4.4dB                                           | 5.2dB            |

| 16PSK      | 7.5Db     | 8dB                                             | 9dB              |

Table (1) SNR v/s Number of iteration and modulation level

Figure (5) Distribution of number of LDPC decoder iterations for different code rate

Figure (6) Simulated output of Complete work

### Vol. 2 Issue 5, May - 2013

# 5. FUTURE SCOPE

Despite LDPC unique of many floor phenomenon features, the error associated with iterative LDPC decoder is produced as a consequence due to their inability to reach very low bit error rates at low SNRs especially with higher code rate for any data input. We conclude that connected BCH codes serially with LDPC can successfully lower the error floor by a factor( from 32 to 22) at about SNR (from -1dB to 1.8 dB) while supporting the same code rates for a BPSK modulated signal. Certainly low BER (e.g. 10-12) can be achieved ,but this demands huge computational tasks which of course required running the program for days. In other word, better Codes provides better coding gains and higher complexity. The basic idea is that, for each LDPC code decoding failure, we use the hard decisions of the inner LDPC decoding iterations as the input to the successive BCH code decoder until the BCH code decoder succeeds. And also try for the implementation for Audio, video, and Live streaming applications etc.

# **REFERENCES**

- [1] In 2003, "Low-Density Parity Check Codes and iterative Decoding for Long-Haul Optical Communication Systems"

- -Bane Vasic, Senior Member, IEEE, Ivan B. Djordjevic, and Raymond K. Kostuk Member, IEEE, Fellow, OSA

- [2] In 2008, "Concatenated Low-Density Parity-Check and BCH Coding System for Magnetic Recording Read Channel with 4KB Sector Format"

- -Ningde Xie, Wei Xu, Tong Zhang, Erich F.Haratsch, and Jaekyun Moon

- [3] Ningde, Xie. Wei Xu. Tong Zhang. Erich F. Haratsch and Jaekyun Moon," Concatenated lowdensity parity-check and bch coding system for magnetic recording read channel with 4 kb sector

format ", IEEE Transactions On Magnetics, Vol. 44, No. 12, December 2008.

- [4] Matthew, C. Valenti. Shi Cheng. And Rohit Iyer Seshadri, "Digital video broadcasting", Project, West Virginia University, USA. 1993.

- [5] Tom Richardson, "Error floors of ldpc codes", Proc. 41st Allerton Conf. Comm., Control, and Comput., Monticello, IL, 2003.

- [6] H. Pishro-Nik and F. Fekri, "Performance of lowdensity parity-check codes with linear minimum distance," IEEE Trans. Inform. Theory, vol.52, no. 1, pp. 292-300, 2006.

- [7] Yifei Zhang. And William E. Ryan, "Toward low ldpc-code floors: a case study", IEEE Transactions on Communications, Vol. 57, No. 6, Pp.1566-1573, 2009.

- [8] Zhiping Shi. Liang Zhoul. Hong Wen and Shaoqian Li, "Iterative decoding for the concatenation of ldpc codes and bch codes based on chase algorithm", IEEE 6<sup>th</sup> International Conference on ITS Telecommunications Proceedings, 2006.

### **BIOGRAPHY**

- 1. Mr. Naveenkumar M Hanchinamani is pursuing Bachelor's Degree in Telecommunication Engineering from Dayananda Sagar College of Engineering Bangalore. And completed Diploma Electronics & Communication Engg. In RPH Haunsbhavi, Hirekerur.

- 2. Mr. Amaregouda is pursuing Bachelor's Degree in Telecommunication Engineering from Dayananda Sagar College of Engineering Bangalore.

- 3. Mr. Karthik B.S is pursuing Bachelor's Degree Telecommunication Engineering Dayananda Sagar College of Engineering Bangalore.

- 4. Mr.Jayanth.C is working as an Assistant Professor in Dept of Telecommunication Engineering, Dayananda Sager College of Engineering, Bangalore.