### **ECLECTIC - 2020 Conference Proceedings**

# **Hybrid Asymmetrical Multilevel Inverter with 13 Levels and Reduced Switch Count**

Mrs. C. Pitchai<sup>1</sup>, N. Keerthana<sup>2</sup>, A. Sumithra<sup>3</sup>, G. Thulasibrindha<sup>4</sup> <sup>1</sup>Assistant Professor, Department of Electrical and Electronics Engineering, <sup>2, 3, 4</sup>Student, Department of Electrical and Electronics Engineering, ACT College of Engineering and Technology, Nelvoy, Madurandhagam-603 107, Tamil Nadu, India

Abstract:- This paper introduces a method to enforce balanced power distribution between (1:2:3) the stages of a cascaded MLI using new asymmetric source fed with reduced switch count. In comparison with conventional two-level inverter, multilevel inverter provides more than two levels of voltage to achieve high power, smoother and less distorted alternating voltage by using several semiconductor switches and lower level DC voltages as input. The MLI has been enforced for reducing the bulkiness if the LC filters size as well as the cost of the system. Since the inverter is fed by a three DC sources, asymmetry is enforced providing multiple redundant switching patterns to synthesize an output signal of

Keywords: MLI, PWM, CHB, HVDC based asymmetric switch

#### 1. INTRODUCTION

In last year's, multilevel inverters (MLI) have become a competitive solutions against conventional inverters based on pulse-width modulation (PWM), which are still very popular in the market [1]. Now a day's the demand of MLI growing rapidly in the field of power conversion i.e., from DC/AC, AC/DC & DC/DC, conversion of frequency with varying output etc. and their application. MLI can be used for DC/AC motor drives, Utility interface system, uninterrupted power supplies (UPS), high voltage DC power transmission (HVDC), flexible AC transmission system (FACTS), static var compensators (SVC), active filters (AF), electric and hybrid electric vehicles and integration and utilization of renewable energy sources [2]. The converter offers better and more sinusoidal output voltage means low output voltage IHD, high efficiency and power factor. In conventional topology, there are mainly three types of MLI:1) diode clamped type, 2) Flying capacitor type (single common source and neutral pint clamped), 3) CHB type. Diode clamped type inverters have the advantages of increased efficiency, simple control and less harmonic content with increased level without the necessity of filters [3]. But having drawbacks due to using excessive number of clamping diodes with increasing steps and difficult to control real power flow of individual converter in multi converter system. Compared to other topologies, cascaded multilevel inverter has advantages of using least number of components to achieve the same amount of voltage level [4]. Another advantages of using circuit layout and possible packaging due to having same structure of each level and also having soft switching techniques [5].

The CHB topology has attracted researches attention because of some shortcomings associated with NPC and FC including large capacitor requirement, unbalancing in the dc links and large stress on the power switches. Cascaded multilevel inverter could be classified in two types: 1) symmetrical CHB, 2) asymmetrical CHB. Symmetrical CHB converter uses a number of equal dc voltage sources while asymmetrical counterpart uses unequal voltage sources [6]. It also improves the reliability by reducing the number of dc voltage sources. Several works has been carried out literature notably on novel topologies for asymmetric and symmetric configuration using isolated dc voltage sources and the connection of Hbridge circuits. The present paper suggests a new hybrid MLI topology with reduction in number of power switches along with dc sources [8].

#### 2. PROPOSED SYSTEM

The present paper suggests a new hybrid MLI topology with reduction in number of power switches along with dc voltages sources. The presented asymmetric MLI overcomes the drawbacks of the conventional system works on high switching frequencies as well as high count of input DC sources are required. Addition H-bridge is required to generate pure sine AC waveform with less harmonics distortion. The switches count can be reduced from the conventional cascaded inverter. The simple PWM technique is utilized for the generation of pulses to the MLI switches which increases the simplicity of the control. The concept of reduce device count is to reduce the size of hardware as well as cost and complexity of hardware.

## 3. METHODOLOGY

- PWM Technique

- CHB Technique

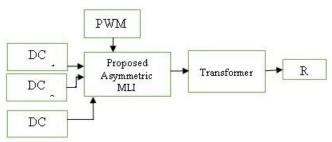

# 4. BLOCK DIAGRAM

The proposed system block diagram consists three asymmetrical PV based DC source in the ratio 1:2:3 fed to the proposed asymmetric MLI. The asymmetric MLI have the capability of producing 13 level of output voltage with the help of simple PWM control techniques [10]. The transformer is used for the isolated protection circuit. The proposed asymmetric MLI consists of dual unit structure. One unit is responsible for the generation of voltage levels and other is responsible for the generation of AC waveform by changing the polarity of current flow through the load. The different equations for the generalized assembly of the proposed topology for N number of levels are given as:

- 1. N (SWITCH) =1/3(N+17)

- 2. N (SOURCE) = 1/6(N+5)

ISSN: 2278-0181

Fig.1 Block Diagram of MLI

The proposed converter operated at low switching frequency of 5000Hz which reduces the stress on the switches.

#### 5. CONCLUSION

This paper presented a modified asymmetric MLI with isolated protection which also implemented with simple PWM control technique. The solar asymmetrical source is utilized by which the eco-friendly characteristics as well as cost effective solution are achieved. The presented topology has the advantages of less reduced switch count which increases the cost effectiveness of the system. The proposed MLI exhibits the less harmonic distortion with the value of 5.86% and it can operate at low switching frequency which increases the reliability of the system. The power efficiency is also increase with balance power distribution systems.

## 6. REFERENCES

- [1] O. Lopez-Santos, C. A. Jacanamejoy-Jamioy, D. F. Salazar-D'Antonio, J. R. Corredor-Ramírez, G. Garcia and L. Martinez-Single-Phase Transformer-Based Cascaded Asymmetric Multilevel Inverter With Balanced Power Distribution," in *IEEE* 98182-98196,2019.Doi: Access. vol. 7. pp. 10.1109/ACCESS.2019.2930230.

- [2] M. Malinowski, K. Gopakumar, J. Rodriguez, M.A. Pérez, "A Survey on Cascaded Multilevel Inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, 2010, pp. 2197-2206.

- J. Rodriguez, J.S. Lai, F.Z. Peng. "Multilevel Inverters: A Survey of Topologies, Controls and Applications," IEEE Trans. Ind. Electron., 2002, vol. 49, no. 4, pp. 724-738.

- [4] E. Colak, R. Kabalci, R. Bayindir. "Review of multilevel voltage source inverter topologies and control schemes," Energy Conversion and Management, 2011, vol. 52, pp. 1114-1128.

- [5] A.K. Panda, Y. Suresh, "Performance of cascaded multilevel inverter by employing single and three-phase transformers," IET Power Electron., vol. 5, no. 9, pp. 1694-1705, 2012.

- A.K. Panda, Y. Suresh, "Research on cascade multilevel inverter with single DC source by using three-phase transformers," Electrical Power and Energy Systems, vol. 40, 2012, pp. 9-20.

- [7] J. Pereda, J. Dixon, "High-Frequency Link: A Solution for Using Only One DC Source in Asymmetric Cascaded Multilevel Inverters," IEEE Trans. Ind. Electron., vol. 58, no. 9, 2011, pp. 3884-3892.

- E. Babaei, M. Sadegh, "Asymmetric Cascaded Multilevel Inverter with Charge Balance Control of a Low Resolution Symmetric Subsystem," Energy Conversion and Management, 2010, vol. 51, pp. 2272-2278.

- [9] Farakhor, R. Reza Ahrabi, H. Ardi and S. Najafi Ravadanegh, "Symmetric and asymmetric transformer based cascaded multilevel inverter with minimum number of components," IET Power Electron., vol. 8, no. 6, pp. 1052-1060, Jun. 2015.

- [10] M.R. Banaei, H. Khounjahan, E. Salary, "Single-source cascaded transformers multilevel inverter with reduced number of switches," IET Power Electron., vol. 5, no. 9, 2012, pp. 1748-1753.