# FPGA based Efficient Error Reduction Address Generator for WiMAX DEINTERLEAVER

Sakhamura Sravanthi <sup>1,\*</sup> Rajendra Prasad Somineni<sup>2</sup>

<sup>1,\*</sup> Research Scholar, Department of ECE, Shri JJT University, Jhunjhunu, Rajasthan, India

<sup>2</sup> Professor, Department of ECE, VNR Vignana Jothi Institute of Engineering and Technology, Hyderabad, India

Abstract:- A low-multifaceted nature and novel system is proposed to proficiently execute the location age hardware of the 2-D deinterleaver utilized in the WiMAX trans collector utilizing the Xilinx field-programmable Gate Arrray (FPGA). The floor capacity related with the usage of the means, required for the stage of the approaching piece stream in channel interleaver/deinterleaver for IEEE 802.16e standard is hard to actualize in FPGA. A basic calculation alongside its scientific foundation created in this brief, takes out the prerequisite of floor capacity and accordingly permits low-intricacy FPGA usage. The utilization of an inside multiplier of FPGA and the sharing of assets for quadrature stage move keying, 16-quadrature-amplitude modulation (QAM), and 64-QAM adjustments alongside all conceivable code rates makes our way to deal with be novel and profoundly effective when contrasted and regular look-into table-based methodology. The proposed methodology shows huge improvement in the utilization of FPGA resources.

Keywords: FPGA, QAM, WiMAX,LUT

## I. INTRODUCTION

BROADBAND wireless access (BWA) is consistently turning into an all the more provoking contender to the customary wired last mile get to advancements. IEEE has created benchmarks for versatile BWA (IEEE 802.16e) prevalently alluded to as portable WiMAX. The direct interleaver utilized in the WiMAXtransreceiver assumes an essential job in limiting the impact of burst error. In this short, a novel, low-multifaceted nature, fast, and asset effective location generator for the divert deinterleaver utilized in the WiMAXtransreceiver disposing of the prerequisite of floor capacity is proposed. Not many works identified with equipment execution of the interleaver/deinterleaver utilized in a WiMAX framework is accessible in the writing.

The work in shows the gathering of approaching information streams into the square to lessen the recurrence of memory access in a deinterleaver utilizing a traditional look-into table (LUT)- based CMOS address generator for WiMAX based execution of location generator for IEEE 802.16e channel interleaver with just a 1/2 code rate. In the creators have portrayed a limited state machine (FSM)- based location generator of the equivalent interleaver for all reasonable code rates and tweak schemes.It has made 2-D interpretation of the capacities utilized in WiMAX channel deinterleaver to guarantee effective equipment engineering.

Be that as it may, the determinations in don't unmistakably clarify the structure issues, especially for 64-quadrature-plentifulness adjustment (QAM). Equipment execution of floor capacity is mind boggling and expends anomalous huge measure of assets. Customary LUT-based system is seen as ugly from numerous angles, for example, gradualness in activity, utilization of enormous rationale assets prompting wastefulness in asset usage, and so forth. A near report with a LUT-based method affirms the prevalence of our proposed plan. As contrasted and the convoluted and long articulations, especially for 6-QAM and 64-QAM, because of the 2-D interpretation in a conservative and easy to use scientific portrayal and consequent calculation is proposed.

The numerical articulations have officially been demonstrated utilizing. Our proposed calculation when acknowledged by computerized equipment brings about low-multifaceted nature design for the location generator contrasted and winning system. A nitty gritty perspective on the proposed equipment looked at. To make the plan minimal, the creators received advancement by sharing the basic equipment between the modules for quadrature stage move keying (QPSK), 16-QAM, and 64-QAM. This engineering is displayed in VHDL and executed on the Xilinx Spartan-3 FPGA. Programming recreation utilizing ModelSim is performed to confirm the usefulness of the proposed calculation and equipment.

FPGA execution results alongside their conceivable correlation with ongoing comparative work have been made. In this short, utilization of FPGA's inserted multiplier gives execution improvement by lessening interconnection delay, proficient asset utilization, and lesser power utilization contrasted and a configurable rationale square based multiplier. Our work demonstrates improvement over the LUT procedure to the tune of roughly 49% as far as most extreme working recurrence.

## 2. LITRATURE SURVEY

The immediate usage of interleaver works in WiMAX propsed R. Asghar et.al isn't equipment productive because of essence of complex capacities. Likewise the ordinary strategy for example utilizing recollections for putting away the change tables is silicon expending. This work shows a 2-D change for WiMAX channel interleaver capacities which lessens the general equipment unpredictability to process the interleaver addresses on the fly. A completely reconfigurable engineering for location

Vol. 10 Issue 04, April-2021

age in WiMAX channel interleaver is displayed, which devour 1.1 k-entryways altogether. It tends to be arranged for any square size and any balance plan in WiMAX. The exhibited design can keep running at a recurrence of 200 MHz, along these lines completely supporting high transmission capacity prerequisites for WiMAX.

Kuo net.al presents test estimations of the contrasts between a 90-nm CMOS field programmable entryway exhibit (FPGA) and 90-nm CMOS standard-cell applicationspecific coordinated circuits (ASICs) regarding rationale thickness, circuit speed, and power utilization for center rationale. We portray the procedure by which the estimations were gotten and demonstrate that, for circuits containing just look-into table-based rationale and flip-slumps, the proportion of siliconarea required to actualize them in FPGAs and ASICs is by and large 35. Current FPGAs likewise contain "hard" squares, for example, multiplier/collectors and square memories.Li et.al alters the IEEE 802.16 Wireless MAN-OFDMA determination to give a propelled air interface to activity in authorized groups. It will meet the cell layer prerequisites of IMT-Advanced cutting edge versatile systems. It will be intended to give altogether improved execution contrasted with other high rate broadband cell organize frameworks.

Bijoy Kumar Upadhyaya et.al proposed equipment model comprises of limited state machine based location generator and advanced FPGA's inserted asset based memory. The limited state machine based location generator of the interleaver shows better execution regarding greatest working recurrence, and FPGA asset usage contrasted with existing FPGA procedures. Utilization of FPGA's inserted memory offers points of interest like diminished access time, lesser land inhabitance of circuit load up and lower control utilization than outside memory based systems. Assessed control utilization and programming recreation of both location generator and the total interleaver are likewise given. Our structure is really founded on IEEE 802.16e standard where all the code rates and tweak plans for WiMAX have been joined. Likewise our methodology bolsters calculation of interleaver addresses progressively.

#### 3. EXISTING FRAMEWORK

Symmetrical Frequency Division Multiplexing (OFDM) strategy offers promising arrangement that has increased colossal research enthusiasm for late years because of its high transmission capacity and mitigating the antagonistic impacts of Inter Symbol Interference (ISI) and Inter Channel Interference (ICI) capacity. In an OFDM framework, the information is isolated into various parallel sub-streams at a diminished information rate, and each is balanced and transmitted on a different symmetrical subcarrier. This builds image term and improves framework power. OFDM is accomplished by giving multiplexing on clients' information streams on both uplink and downlink transmissions. OFDM is the major structure square of the IEEE 802.16 standard.

In this framework, the info paired information stream got from a source is randomized to avert a long grouping of 1s and 0s, which will reason timing recuperation issue at the beneficiary. Pseudo Random Binary Sequence (PRBS) is utilized in which randomization is finished by modulo 2 expansion of the information with the yield of the PBRS itself [5]. The randomized information bits are from there on encoded utilizing Reed Solomon (RS) encoder pursued by Convolutional Coder(CC). The previous is reasonable for adjustment of blasted kind of mistake though the later is for irregular blunder. After RSCC encoding all encoded information bits will be interleaved by an uncommon sort of square interleaver. From that point, information goes through the mapper obstruct in which tweak happens. The subsequent information images are utilized to build one OFDM image by performing Inverse Fast Fourier Transform (IFFT). In the beneficiary, reverse squares are applied which perform DFT, de-mapping, de-interleaving, unraveling and de-randomizing activities in successive way to get back the first information grouping.

In existing framework to execute the location generator utilized in OFDM-WiMAX de-interleaver. The customary Look-Up Table (LUT) based strategy for location age has been overhauled to utilize the memory squares proficiently. During this work, it has been seen that inside a tweak conspire the location LUT of a littler interleaver profundity is the subset of the location LUT of bigger interleaver profundity in WiMAX de-interleaver address generator. It indicates advancement of roughly 30% over regarding greatest working recurrence.

## 4. PROPOSED FRAMEWORK

The work in exhibits the gathering of approaching information streams into the square to diminish the recurrence of memory getting to a deinterleaver utilizing an ordinary look-into table (LUT)- based CMOS address generator for WiMAX.has depicted an equipment portrayal language (VHDL) based usage of location generator for IEEE 802.16 echannel interleaver with just a 1/2 code rate. Both are tried on the field-programmable door exhibit (FPGA) platform.2-D interpretation of the capacities utilized in WiMAX channel deinterleaver to claimefficient equipment design. In any case, the deductions indo not plainly clarify the structure issues, especially for64-quadrature-adequacy balance (QAM). Hardware execution of floor capacity is intricate and devours strangely enormous measure of assets. Customary LUT-based strategy is seen as ugly from numerous perspectives, for example, gradualness in activity, utilization of huge rationale assets prompting wastefulness in asset use, and so on.

A relative report with a LUT-based strategy affirms the prevalence of our proposed structure. As contrasted and the convoluted and extensive articulations, especially for 16-QAM and 64-QAM, because of the 2-D interpretation in a minimal and easy to understand scientific portrayal and resulting calculation is proposed. The numerical articulation shave officially been

demonstrated utilizing. Our proposed calculation when acknowledged by advanced equipment brings about low-multifaceted nature design for the location generator contrasted and winning system. An itemized perspective on the proposed equipment contrasted and is introduced.

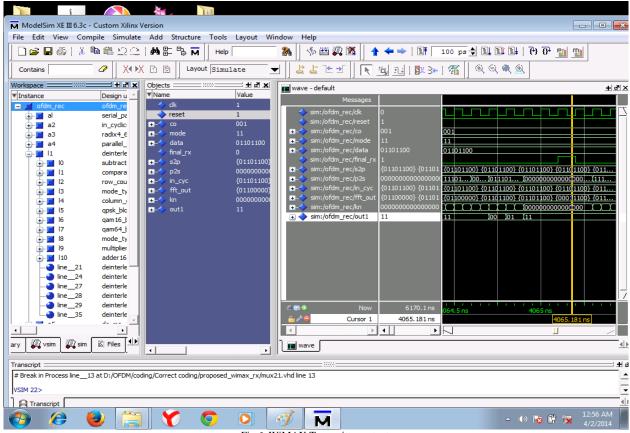

Programming reproduction utilizing ModelSim is performed to confirm the usefulness of the proposed calculation and equipment. FPGA execution results alongside their conceivable examination with ongoing comparative work have been made. In this short, utilization of FPGA's implanted multiplier gives execution improvement by decreasing interconnection delay, productive asset use, and lesser power utilization contrasted and a configurable rationale square based multiplier. Our work demonstrates advancement over the LUT system to the tune of around 49% as far as most extreme working recurrence.

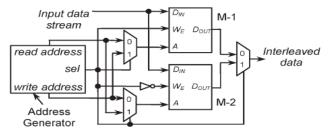

Fig.1. Block diagram of the WiMAX transreceiver.

### 4.1 RANDOMIZER

In this framework, the info double information stream got from a source is randomized to forestall a long grouping of 1s and 0s, which will reason timing recuperation issue at the beneficiary. Psudeo Random Binary Sequence (PRBS) is utilized in which randomization is finished by modulo 2 expansion of the information with the yield of the PBRS itself.

## 4.2 RS-CC CODER

The randomized information bits are from that point encoded utilizing Reed Solomon (RS) encoder pursued by Convolutional Coder (CC). The formet is reasonable for redress of blasted kind of mistake while the later is for arbitrary blunder.

## 4.3 INTERLEAVER/DEINTERLEAVER

The channel interleaver permutes the encoded bit stream to diminish the impact of burst mistake. When convolutional turbo code (CTC) is utilized for FEC, being discretionary in WiMAX, the channel interleaver isn't required, since CTC itself incorporates an interleaver inside it. Adjustment and development of symmetrical recurrence division multiplexing images are performed by the two consequent squares, specifically, mapper and converse quick Fourier transform.

Fig. 2. Block diagram of interleaver/deinterleaver structure

## **5.RESULTS AND DISCUSSIONS**

# 5.1 SIMULATION RESULT

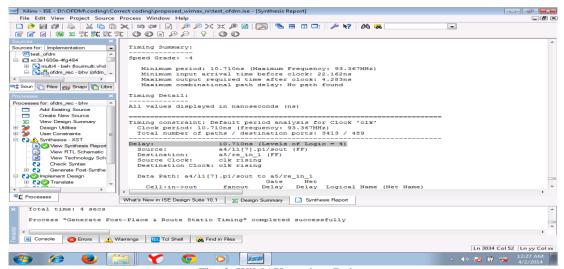

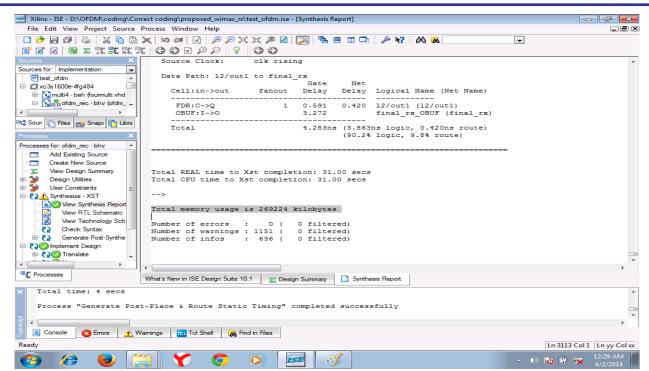

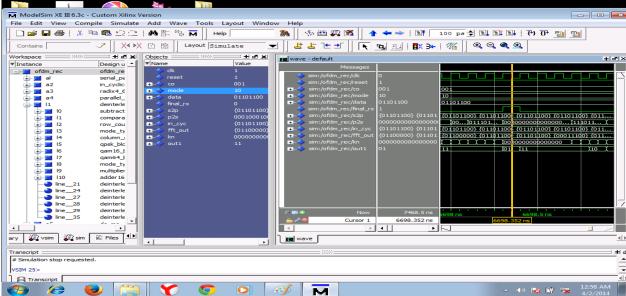

The proposed equipment of the location generator is changed over into a VHDL program utilizing the Xilinx ISE. Reproduction results are acquired for all admissible regulation sorts and code rates utilizing ModelSim XE-III and a piece of the equivalent for Ncbps = 576-bits, 3/4 code rate, and 64-QAM has been displayed in Table-1. The underlying bit of Table demonstrates the last piece of addresses for first column (j = 1), and the last part (from ruler) demonstrates the addresses for second line (j = 2).

| Logic Circuit Used | Quantity | Logic Circuit Used | Quantity |  |

|--------------------|----------|--------------------|----------|--|

| 16×3-bit ROM       | 1        | 4-bit register     | 1        |  |

| 64×3-bit ROM       | 1        | 6-bit register     | 1        |  |

| 10-bit adder       | 1        | 4-bit 4-to-1       | 3        |  |

| 18-bit adder       | 2        | 4-bit 8-to-1       | 1        |  |

| 18-bit subtractor  | 2        | 6-bit 4-to-1       | 3        |  |

| 4-bit adder        | 1        | 6-bit 8-to-1       | 1        |  |

| 6-bit adder        | 1        |                    |          |  |

|                    |          | Multiplier         |          |  |

Table 1:VHDL synthesis report

Fig. 3. WiMAX receiver Delay

Fig .4. Total Memory Usage

Fig 5.WiMAX receiver output

Fig.6. WiMAX Transmitter output

|                   | LUT  | SLICES | DELAY    | POWER(W) |

|-------------------|------|--------|----------|----------|

| Existing_wimax_rx | 2290 | 1961   | 10.710ns | 5.465    |

| Proposed_wimax_rx | 289  | 235    | 10.710ns | 1.673    |

Table 2: Comparison between the proposed and lut-based technique

# 6. CONCLUSION

An epic calculation alongside its numerical detailing, including verification for location age hardware of the WiMAX channel deinterleaver supporting all conceivable code rates and adjustment designs according to IEEE 802.16e. The proposed calculation is changed over into an improved advanced equipment circuit. The equipment is actualized on the Xilinx FPGA utilizing VHDL. Examination of our proposed work with a regular LUT-based technique and furthermore with an ongoing work show critical enhancement for asset usage and working frequency

#### 7. REFERENCES

- [1] A. A. Khater, M. M. Khairy, and S. E.-D.Habib, "Efficient FPGA implementation for the IEEE 802.16e interleaver," in *Proc. Int. Conf. Microelectron.*, Marrakech, Morocco, 2009, pp. 181–184.

- [2] B. Li, Y. Qin, C. P. Low, and C. L. Gwee, "A survey on mobile WiMAX," IEEE Commun. Mag., vol. 45, no. 12, pp. 70–75, Dec. 2007.

- [3] B. K. Upadhyaya, I. S. Misra, and S. K. Sanyal, "Novel design of addressgenerator for WiMAX multimode interleaver using FPGA based finitestate machine," in *Proc. 13th Int. Conf. Comput. Inf. Technol.*, Dhaka, Bangladesh, 2010, pp. 153–158.

- [4] B. K. Upadhyaya and S. K. Sanyal, "An improved LUT based reconfigurable multimode interleaver for WLAN application," *Int. J. RecentTrends Eng. Tech.*, ACEEE, vol. 6, no. 2, pp. 183–188, 2011.

- I. Kuon and J. Rose, "Measuring the gap between FPGAs and ASICs,"in Proc. Int. Symp. FieldProgramm. Gate Arrays, Monterey, CA, USA,2006, pp. 21–30.

- [6] IEEE Standard for Local and Metropolitan Area Networks—Part 16: AirInterface for Fixed Broadband Wireless Access Systems—Amendment 2,IEEE Std. 802.16e-2005, 2005.

- [7] J. G. Andrews, A. Ghosh, and R. Muhamed, Fundamentals of WiMAX: Understanding Broadband Wireless Networking. Upper Saddle River, NJ, USA: Prentice-Hall, 2007, ch. 8.

- [8] Local and Metropolitan Networks—Part 16: Air Interface for FixedBroadband Wireless Access Systems, IEEE Std. 802.16-2004, 2004.

- [9] M. N. Khan and S. Ghauri, "TheWiMAX 802.16e physical layer model," in Proc. IET Int. Conf. Wireless, Mobile Multimedia Netw., Mumbai, India, 2008, pp. 117–120.

- [10] R. Asghar and D. Liu, "2D realization of WiMAX channel interleaverfor efficient hardware implementation," in *Proc. World Acad. Sci. Eng. Technol.*, Hong Kong, 2009, vol. 51, pp. 25–29.

- [11] W. Konhauser, "Broadband wireless access solutions—Progressive challengeand potential value of next generation," Wireless Pers. Commun., vol. 37, no. 3/4, pp. 243–259, May 2006.

- [12] Xilinx Spartan-3 FPGA Family: Complete Data Sheet, Xilinx, Inc., SanJose, CA, USA, 2012.

- [13] Y. N. Chang and Y. C. Ding, "A low-cost dual mode de-interleaverdesign," in Proc Int. Conf. Consum. Electron., 2007, pp. 1-2.