# Design & Study of Low-Dropout Voltage Regulators for Low-Voltage VLSI Devices.

Shruthi L S

M. Tech, VLSI and Embedded Systems, ECE

T. John Institute of Technology

Bangalore, India

Mrs. Roopashree. K. S

Assistant professor, ECE

T. John Institute of Technology

Bangalore, India

**Abstract**— This brief presents a design and study of low-voltage Low-dropout Voltage regulators for low-voltage VLSI devices, which can achieve operation below 1V, fast transient response, high power supply rejection with a low quiescent current under a wide range of operating conditions. The proposed LDO regulator was designed and fabricated using 90nm CMOS technology. The area and the loss of power can be minimized. In addition, a maximum output variation for a load transient, and a maximum current efficiency was achieved. Using the bipolar transistor technology or a complex circuit to achieve a high PSR at the expense of a high quiescent current however, unnecessary for the post regulator of a general purpose switching regulator. The dynamic biasing technique is widely adopted by conducting a very small quiescent current under a light load condition. This inevitably sacrifices the transient response during a light to heavy load transition.

**Keywords**— Low-Dropout (LDO)regulator, Fast transient low voltage, small area, maximum current efficiency, maximum dynamic range, reduction in power loss

## I. INTRODUCTION

Extremely low quiescent current power management circuits are highly desirable for battery powered applications, as any current drained from the battery would encroach into the remaining battery capacity. But unlike many low power applications like passive RFIDs, portable multimedia electronics such as tablets, laptops and phones, require their power supply modules to source a much wider output current range to support the ever increasing functionality and processing power in the gadgets. Low-dropout regulators (LDOs) are one of the most widely used power supply modules for noise sensitive analog. And LDO are key components of SOC application. A switching pre-regulator is usually followed by a low dropout (LDO) regulator to provide a regulated power source for noise sensitive blocks. It has a simple architecture and a fast-responding loop, which makes it the best candidate to implement these post regulators.

The design in [2],[3],[11] is focused on enhancing the transient response and drive a large current. The LDO regulators proposed in [11] achieved a high PSR over a wide frequency range.

## II. ARCHITECTURE AND DESIGN OF PROPOSED LDO REGULATOR

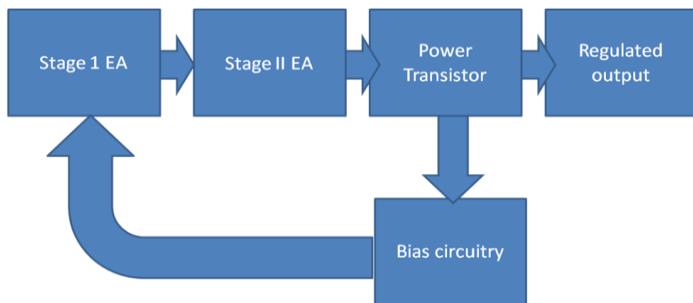

A basic LDO regulator composed of an EA, a power MOS transistor ( $M_p$ ), biasing circuit, and a feedback network as shown in fig.1. An off chip output capacitor used to check the output variation during the load transient. The challenges and the concept of designing a low-voltage LDO regulator are briefly discussed below.

### A. Input voltage and low quiescent current

A high loop gain is mandatory in LDO regulator design to achieve optimum performance values as accurate output and PSR. A low supply voltage and output resistance reduction induced by a shrinking technology limit the achievable gain of the EA.

To achieve a low-voltage operation, an error amplifier with more than three stacked transistors between the supply voltage and ground is preferred. The EA requires a wide output swing to minimize the size of pass device and hence ease the requirement on voltage change (slew rate) of the EA.

### B. Fast transient Response

The transient response is the voltage variation and recovery time during the load current transient. The voltage variation is more important than the recovery time, as even a small output voltage variation can cause severe performance degradation to the load circuit operation. To reduce the output voltage variation, both a large close loop bandwidth of the LDO regulator and a large output current slew rate of the EA is required.

Increasing the closed loop bandwidth may, however affect the pole/zero locations and the circuitry may become too complex, consuming more quiescent current. The concept of the transconductance amplifier is shown.

Fig.1 Block diagram of proposed LDO regulator

### C. power supply rejection

To provide a clean and accurate output voltage with a low voltage level, noise suppression is needed. It is difficult to achieve a high loop gain with a low supply voltage. The concept of resource sharing power noise cancellation mechanism as shown in Fig.1 The first stage EA attenuates the power noise ,Second stage rejects the common mode noise at its inputs, and creates a replica of the supply noise at the output.

#### D. *Small area*

In a low voltage LDO regulator design several performance enhancing auxiliary circuits and a large  $M_p$  occupy space considerably. To support a wide load current range and a wide output voltage range, the  $M_p$  may enter the triode region. Similarly, the LDO regulator can respond to the load current transient in time for such a wide range of operating conditions.

### E. Stability

The dominant pole for an off-chip capacitor compensated LDO regulator, exists at the output node. As a large  $M_p$  contributes the first nondominant pole( $P_g$ ) at a relative low frequency,a large equivalent series resistance of  $C_L$  is required to generate a low frequency zero to cancel  $p_g$ .A wide output swing EA can reduce the size of the  $M_p$  implying that pole zero cancellation is taking place at a higher frequency with a related small  $R_{esr}$ .

### III. CIRCUIT REALIZATION AND SIMULATION RESULTS

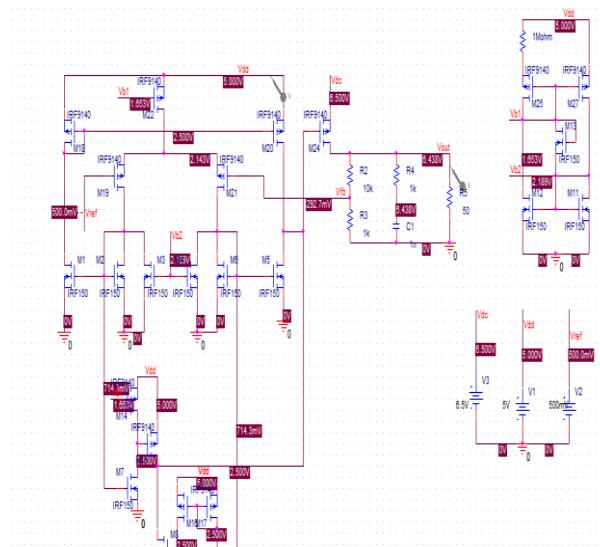

To achieve the required goals of compact and low-voltage operation while achieving a fast transient response, low  $I_Q$  and high PSR, are optimized. The circuit schematic is shown in Fig.2. We first apply the simple symmetric OTA as the EA.

Fig. 2 Circuit schematic of the proposed LDO

The OTA type EA requires no compensation capacitor ,and operates at a minimum supply voltage equal to one threshold voltage plus twice the overdrive voltage.Thus,the EA can

$$\begin{aligned}

A_{EAO} &= g_{m2} \times A \times (r_{07} || r_{09}) \\

&\approx g_{m2} \times A \times r_{09} \\

&= (2 \text{Id}2 \div V_{ov2}) \times A \times (1 \div \lambda_9 \times A \times I_{d2}) \\

&= 2 \div (V_{ov2} \times \lambda_9)

\end{aligned} \tag{1}$$

Where we assume  $(r_{07} \parallel r_{09})$  and let  $\{I_{d2}, V_{ov2}, A\}$  represent the bias current, overdrive voltage and the current ratio between the first and second stages of EA. The  $A_{EAO}$  in (1) is too low to achieve a fast transient response and high PSR. Therefore we apply a current splitting technique shown in Fig.3. to boost the gain by maintaining  $g_{m2}$  and increasing  $r_{09}$ . Thus, the gain of the modified EA ( $A_{EAM}$ ) is boosted by a factor of  $1/B$  as follows:

$$A_{EAM} \approx g_{m2} \times A \times r_{09}$$

$$= (2Id2 \div Vov2) \times A \times (1 \div \lambda_9 \times A \times B \times I_{d2})$$

$$= A_{FAO} \div B$$

Where  $B$  is the current splitting ratio and is  $<1$ . The gain boosted OTA-based EA improves the loop gain of the LDO regulator, which in turn enhances the PSR performance. The two equivalent resistors between the output nodes ( $V_x$  and  $V_y$ ) of the first stage of the EA and the ground

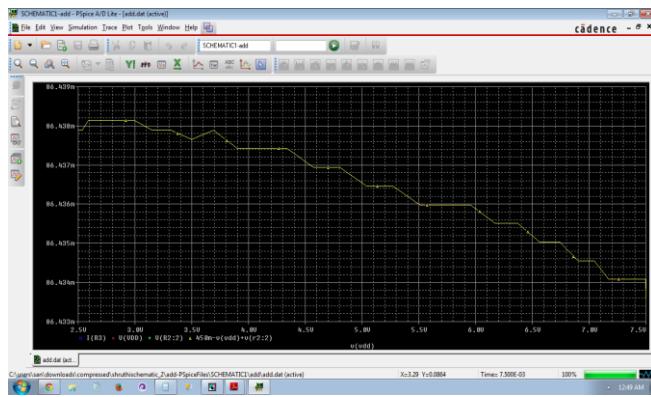

Fig.3. Measurement of dropout voltage with the change in input voltage

Measurement of dropout voltage with the change in input voltage Fig.3. We first assume that the power noise is propagated by stage 1\_EATA through the common mode signal  $V_{icm}$  and causes fluctuation on  $V_{g6}$ . The output  $V_g$  induced by  $V_{icm}$  is, given by

$$\begin{aligned}

V_g &= (g_{m7}V_{g6} - g_{m9}V_{icm})(ro7\|r_{o9}) \\

&\approx (g_{m7}(g_{m8} - g_{m6}) - g_{m7}V_{icm})(ro7\|r_{o9}) \\

&= ((g_{m7} - g_{m6})g_{m8} - g_{m9})V_{icm}(ro7\|r_{o9}) \\

&\approx 0

\end{aligned} \tag{3}$$

Where we assume that  $M_{EA8}$  and  $M_{EA9}$  are matched devices. To cause  $g_{m6}$  to be close to  $g_{m7}$ , the channel length of  $M_{EA6}$  and  $M_{EA7}$  are selected to be five times the minimum length to reduce the effect of channel length modulation. then, we ground both the nodes  $V_x$  and  $V_y$  and input the power noise from the power supply. The small signal model shown at the top of Fig.3 is used to show how the power noise is replicated to  $V_g$ . The result is given as

$$\begin{aligned}

V_g &= V_{dd}(r_{o9} \div (r_{o7} + r_{o9})) + i_{dd}(ro7\|r_{o9}) \\

&\approx V_{dd}(r_{o9} \div (r_{o7} + r_{o9})) + V_{dd}(ro7r_{o9} \div ro7 + ro9) \\

&= V_{dd}

\end{aligned}$$

As the frequency of the power noise increases, the small signal model shown in Fig.3 is no longer valid as the equivalent impedance of the parasitic capacitance of  $M_p$  becomes finite and can no longer be ignored.

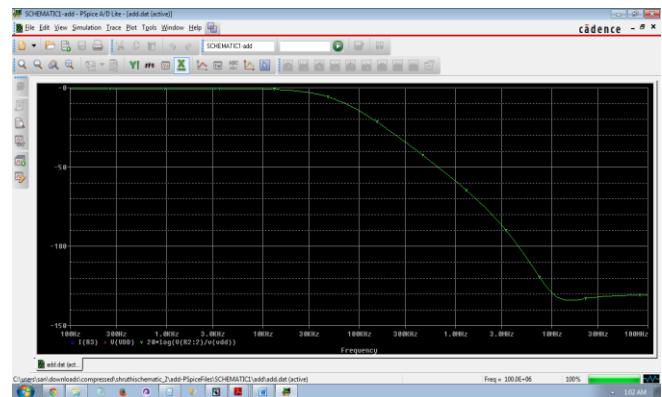

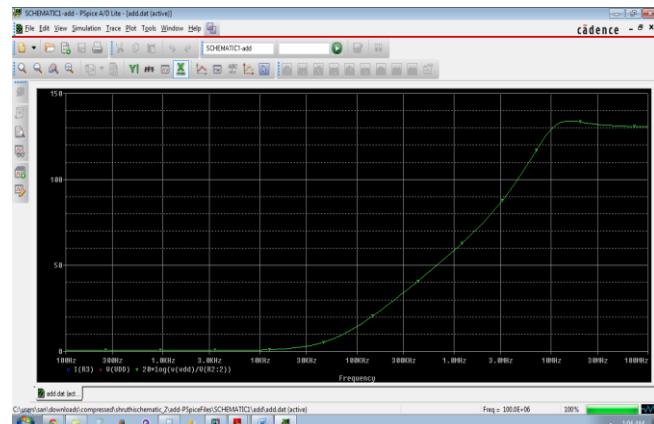

Fig.4. Simulated frequency response of the proposed LDO regulator

The proposed LDO regulator shown in Fig.2 has three poles( $P_o, P_x$  and  $P_g$ ) and one zero( $Z_{esr}$ ), and the simulated frequency response of the loop gain for the different load currents , output voltage and series resistance are shown in Fig.4. The dominant pole is  $P_o$  due to the large off-chip compensation capacitor  $C_L$ .The second dominant pole  $P_g$  is located at a relatively high frequency as the wide output swing of the EA reduces the size of the  $M_p$ .Thus,  $P_g$  can be easily cancelled by the zero with the series resistor.The third pole  $P_x$

Is far beyond the UGF because of the simple architecture of the OTA based EA, and therefore does not affect the stability.Fig.4. guarantees the stability of the proposed LDO regulator for a wide range of operating conditions.

Fig.6. shows the measured PSR performance

#### IV. RESULTS

Fig.2. shows the schematic of the low dropout low voltage regulator. The above schematic is created in PSPICE. Fig.4. shows the simulation results of the low dropout regulator.

#### ACKNOWLEDGMENT

We take this opportunity to express our deepest gratitude and appreciation to all those who have helped us directly or indirectly towards the successful completion of this paper.

#### REFERENCES

- [1] P. Hazucha , T. Karnik, B.A .Bloechel, C.Parsons, D. Finan, and S. Borkar "Area efficient linear regulator with ultra fast load regulation ",IEEE J. Solid State circuits,vol.40,no.4,Apr.2005

- [2] Y-H .Lee Y-Y Yang,K.H.Chen,Y.H.Lin,S.J.Wang,K.L.Zheng,P.F.Chen,C.Y.Hsieh,Y. Z.Ke. Y.K. Chen. and C.C. Huang," A DVS embedded system power management for high efficiency integrated SOC in UWB system,"IEEE J. Solid-state circuits, vol. 45,no.11,pp.2227-2238.nov. 2010

- [3] C. Chen, J. H. Wu, and Z.X.Wang,"150mA LDO with self-adjusting frequency compensation scheme, "Electron. Lett,vol.47,no.13 pp.767-768 june 2011.

- [4] J.H u ,B. H u, Y. Fan ,and M .Ismail, "A 500nA quiescent,100mA maximum load CMOS low-dropout regulator" ,IEEE. Conf. Electron circuits Syst., Dec. 2011 pp.386-389.

- [5] C. Zhan and W. H. K i, "An adaptively biased low drop out regulator with transient enhancement",Conf.,2011,pp-117-118.

- [6] M.EL- Nozahi. A. Amer.j. Torres. K. Entesari , and E. Sanchez-Sinencio, "High PSR low dropout regulator with feed forward ripple cancellation technique" IEEE J. Solid State circuits,vol.45,no.3,pp.565-577.Mar.2010.

- [7] M. Al-Shyoukh, H.Lee, and R.perez."A transient enhanced low quiescent current low dropout regulator with buffer impedance attenuation", IEEE J. Solid State circuits,vol.42,no.8,pp.1732-1742.Aug.2007.

- [8] Y.-H.Lam and W-H.Ki "A 0.9V 0.35m adaptively biased CMOS LDO regulator with fast transient response" in proc. , IEEE int.. Solid State circuit conf,pp.442-443.Feb.2008.

- [9] A.Garimella M.W.Rashid and P.M.Furth,"Reverse nested miller compensation using current buffers in a three-stage LDO" IEEE Tran.circuit syst.II.Exp.Briefs,vol.57,no.4,pp.250-254.Apr.2010.

- [10] A.P.Patel and G.A.Rincon-Mora,"High Power Supply Rejection current mode low dropout regulator" IEEE Tran..circuits syst.II.Exp.Briefs,vol.57,no.11,pp.868-873.Nov.2010.