# Adders: The Basic Arithmetic Building Block

# Jaimin Desai Dept of Electronics Engineering Shah and Anchor Kutchhi Engineering College Mumbai, Maharashtra, India

Abstract—This paper provides an overview of basic adders used for arithmetic calculations. Different types of adders are presented on the basis of Area they occupy in terms of No. of Gates are used. Adders are being used as the basic building block of arithmetic calculations. The detail literature survey has done for different types of the adders and also compared with each other to find out the suitable adder for a designated task.

Keywords— Full Adder(FA),  $P_i$  and  $G_i$  signals, Calculation, AND gate, OR gate, Delay, Speed, Area, Cost

# I. INTRODUCTION

When we come across to fast arithmetic calculation the first block which needs to be considered is the Adder. Adder is the key block which calculates addition of all the numbers. In today's fast world we require faster processing adders to save time. On the other hand, we also want that the adders should occupy less area and should consume less power. We have compared different types of adders in this paper to get better idea for selection of adder for a specific application. There are different types of adders which are available. Ripple carry adder being the basic one where the sum and carry are calculated in sequence. To overcome the delay factor, Carry Lookahead adder was developed which reduces the carry value generation time as compared to Ripple carry adder. Carry Select adder which uses both carry lookahead adder and ripple carry adder and is pre-calculating the values of carry and sum. Another type of adder is the Carry Skip adder in which the time is reduced by skipping the few full adder blocks while calculating. Carry save adder is used to add more than two input at a time. Parallel prefix adder which contains the P and G signals and are faster in terms of speed and reduces the delay.

## II. RIPPLE CARRY ADDER(RCA)

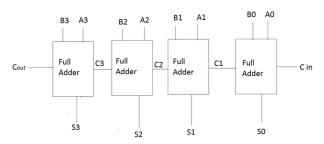

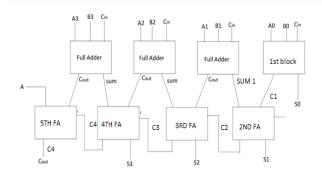

As the name suggest the arithmetic addition is done in the form of ripple. Ripple carry adder consist of Full Adders(FA), but the number of full adders depends on the number of bits to be calculated as shown in Fig.1. Less area is occupied in comparison to other adders, only FA is present as an adding component. The number of inputs are two and the number of output is also two. Speed is low, as output of previous FA needs to be used as the input for next FA. Each FA block generates the Sum as and when the addition between the two input takes place but when it comes to carry the pattern is different. When a carry is generated it flows to the input of the next full adder as an input, and the process of carry generated flowing into the next full adder continues, hence the name is ripple carry adder[1]. Time taken to calculate is more, sum and carry values are calculated by all the FA's. This adder is the basic building block of the adders. It has few advantages like the power consumption is comparatively lower than the

# Nibha Desai Dept of Electronics Engineering Shah and Anchor Kutchhi Engineering College Mumbai,Maharashtra, India

rest of the adders & cost is less as it occupies a smaller area and uses only FA's.

Fig.1 4-Bit Ripple Carry Adder

#### III. CARRY LOOKAHEAD ADDER(CLA)

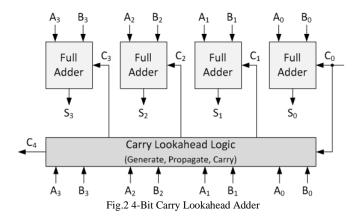

It is the type of adder which was designed to overcome the disadvantages of RCA. The importance about carry lookahead adder is that here delay is much lesser than RCA, the values of sum and carry are calculated by the initial P<sub>0</sub> and G<sub>0</sub> signals, so there is no need to go through all the FA's. Here, Adder propagates and generates signal which are used to calculate the value of carry. The propagate signal is denoted by 'P<sub>i</sub>' and has the formula  $P_i = A_i + B_i$ . And generate signal being denoted by 'Gi' with the formula  $G_i = A_i * B_i$  [2]. The formula for carry is  $C_{i+1} = G_i + P_i * C_i$ . Here 'i' is the bit for which we are calculating the carry. Higher speed than RCA, as CLA uses Propagate(P<sub>i</sub>) and Generate(G<sub>i</sub>) signals, also carry and sum is calculated by using only the first P<sub>0</sub> and G<sub>0</sub> signals which is the main advantage of this adder and we can derive Ci+2 and other carry outputs from those values. Its performance for calculation is at a faster pace but the area occupied is more than RCA, presence of CLA logic and regular RCA along with P and G signals as seen in Fig.2. Also, here the full adders are little bit modified then we normally see in the regular full adders. Cost is higher than RCA, as it has more wiring tracks and area is more than RCA.

ISSN: 2278-0181

#### IV. CARRY SELECT ADDER(CSA)

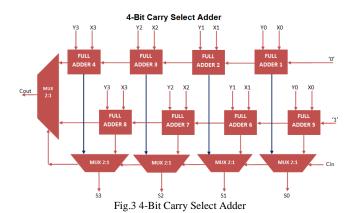

This type of adder is used to overcome the demerits of RCA. Area occupied is more than CLA and twice of RCA, has twice the no. of FA's than RCA & CLA, with 2:1 MUX for selecting the carry. As the name suggest the carry generated is selected on the basis of the Cin provided at the start. Here we use two different carry-in values i.e 0 and 1 as shown in Fig.3 [3]. Traditionally we use one carry value which gets generated from the previous block of the FA, for the calculation of the full adder ahead of it, but here we have carry values of 0 and 1 instead of one carry value. As there are two carry-in values so we use two sets of full adders for calculating the sum and carry for each carry-in values. So, we pre-calculate the sum and the carry values for the particular block. Now on the basis of Cin the sum and carry values are carry forwarded by the Multiplexers, AND and OR gate. And hence we get the sum and carry values. When we consider speed as a factor then it is faster than RCA, carry & sum each have two output values for two possible input values of Cin ie 0 & 1. Depending on the initial value of Cin the value of carry & sum is taken at output. But the delay is more in CSA, although the values are calculated beforehand but the use of twice the no.of FA's along with MUX and AND gate increases the delay. Cost is higher than RCA & CLA, the no.of FA's is double the no.of FA's in RCA, usage of MUX & area occupied is more.

#### V. CARRY SKIP ADDER(CSKA)

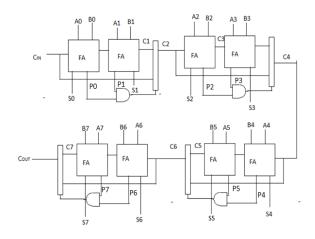

The main function of this type of adder is to skip the carry calculation process. Here adder uses carry lookahead adder for the calculation of Pi and Gi signals as seen in Fig.4. Area is less than CSA, we use FA's, AND logic gates for finding the Propagated signals and 2:1 MUX for selecting the output. All the inputs are processed simultaneously to generate the sum and P<sub>i</sub> signals. The important function is performed by the P<sub>i</sub> signals as they decide whether to skip the carry calculation or not. After the inputs, the sum and P<sub>i</sub> values are generated and adder needs to AND all the Pi values. The output of the AND gate acts as a select line in 2:1 MUX. If the value of the AND gate is 1 i.e. all the P<sub>i</sub> signals are 1 then we use Cin as the carry output and adder skips all the FA's to process the calculation to find carry. But if AND gate value is 0 i.e. any one of Pi signal is 0 then the carry is calculated same like in RCA, that is carry is calculated from LSB to MSB. This type of adder uses both RCA and CLA for calculation [4]. It is faster than RCA,CLA,CSA & CSVA adders, depending upon the Pi

signal output from AND logic block the carry is selected. If output of AND logic block is 1 then Cin(skipping the addition via FA's) is selected as carry and if 0 is the output then carry is generated via FA's. Whereas the delay depends on the value/s of P<sub>i</sub> & AND logic block, if AND logic block gives output as '1' then calculation over FA's are skipped or else calculation happens via FA's. And when it comes to cost, costly than CSA, has FA's like RCA but only one AND logic block and 2:1 MUX.

Fig.4 8-Bit Carry Skip Adder

#### VI. CARRY SAVE ADDER(CSVA)

In this adder rather adding only two inputs at a time and then adding Cin as carry bit, here adder adds Cin as an input along with the other two inputs as seen in Fig.5. Here area is directly proportional to no.of inputs, the FA's occupy less area for less no.of input. If the no.of inputs increase then the no.of FA's increase which increases the area. It is used in application where it is needed to add more than two numbers at a time. No. of FAs used here are less as compared to others types of adders. When it comes to speed, it is slower than CSKA & PPA adders, for more no.of inputs the speed will be low as compared to less no.of inputs. As no.of inputs increase speed decreases. Here adder uses carry of one FA block with sum of the second FA block to get the sum. As per shown in the upper part of the diagram, the important point is that the sum and carry are calculated individually and not simultaneously. Firstly, the sum is calculated without taking carry into consideration. Then adder calculates carry by leaving one space from the LSB side as there is no carry at the start. After the sum and carry values are calculated, then adder adds both of them together to get the final number as per shown in the lower part of the diagram [5]. Delay is variable, as the no.of inputs increases delay also increases, also CSVA is composed of RCA so the delay is more. Cost is less, nominal cost as its basic component is RCA, but cost may increase if no.of input increase.

ISSN: 2278-0181

Fig.5 4-Bit Carry Save Adder

#### VII. PARALLEL PREFIX ADDER(PPA)

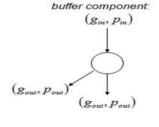

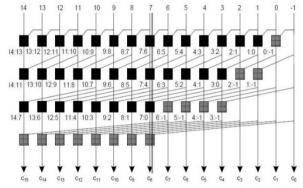

Although CSA and CLA are effective but when the number of bits start to increase, performance is degrading in terms of delay i.e. when it rises to 32, 64 or 128 bits. Brent-Kung adder has a small area in comparison to Kogge-stone adder which has the largest area. Han-Carlson adder has small area as compared to Sklansky adder due to the presence of Logic level, Black and Gray dot operators and Buffers. To overcome this, PPA uses multi-level tree of lookahead structures. Examples of PPA are Brent-Kung, Sklansky, Kogge-Stone(Fig.8) and Han-Carlson adders. These adders work on the basic operators namely black and gray dot. Each of these adders comprises of three blocks. Those are pre-computation (which includes generation of P and G signals) Fig.6, prefix network (which includes dot operators and buffers as shown in Fig.7) [7] and post-computation (which includes the final sum generation block) [6]. Han-Carlson has more speed than all adders mentioned before, as it has lower number of logic levels, wiring tracks are less and the number of prefix network is also less. PPA are categorized on the basis of few factors like logic levels, wiring tracks and fan-outs. Han-Carlson adder has a lesser delay time, various factors like wiring track, logic levels and middle prefix network which include black & gray operator, AND, OR and buffer operations. Each type of adder has its merits and demerits, so depending upon the application the selection of appropriate adder can be done. To calculate the different trade off [7] factors we use the following equation L=log<sub>2</sub>n,l,f and t

Where, Logic levels: L + l(small L)

Fanout: 2<sup>f</sup>+1(one) Wiring track: 2<sup>t</sup>

Cost may increase or decrease depending upon few factors, factors like wiring tracks, operators, buffers and logic level decides the cost of the adder. Lesser the components lesser the price.

$(g_{out}, p_{out}) = (g_{in}, p_{in})$ Fig.7 Buffer Component

Fig.8 16-Bit Kogge-Stone Adder

#### VIII. COMPARISON TABLE

The Table.1 shows the comparison of different types of adders on the basis of few factors like Area, Speed, Delay and Cost which helps us to decide which adders to be used for a specific application. It gives better insights on adders.

| Parameters                             | Area                                           | Speed                                           | Delay                                                                | Cost                                    |

|----------------------------------------|------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------|

| Adders                                 |                                                |                                                 |                                                                      |                                         |

| 1.RCA<br>(ripple carry<br>adder)       | Less area in comparison to other adders.       | Low speed.                                      | Time taken is more.                                                  | Cost is less.                           |

| 2.CLA<br>(carry<br>lookahead<br>adder) | Large Area than RCA                            | Higher speed<br>than RCA                        | Here delay<br>is much<br>lesser than<br>RCA.                         | Cost is<br>higher<br>than<br>RCA.       |

| 3.CSA<br>(carry select<br>adder)       | More Area<br>than CLA<br>and twice of<br>RCA.  | Faster than RCA.                                | Delay is<br>more in<br>CSA.                                          | Cost is<br>higher<br>than RCA<br>& CLA. |

| 4.CSKA<br>(carry skip<br>adder)        | Area is less<br>than CSA.                      | Faster than<br>RCA,CLA,C<br>SA & CSVA<br>adders | Delay<br>depends on<br>the value/s<br>of Pi &<br>AND logic<br>block. | Costly<br>than<br>CSA.                  |

| 5.CSVA<br>(carry save<br>adder)        | Area is directly proportional to no.of inputs. | Slower than<br>CSKA &<br>PPA adders.            | Delay is<br>variable.                                                | Cost is less.                           |

| <b>6.PPA</b> (parallel prefix adder)   | Kogge-<br>Stone adder<br>has largest<br>area.  | Sklansky<br>adder has<br>least speed.           | Han-<br>Carlson<br>adder has a<br>least delay<br>time.               | Cost is variable.                       |

Table.1 Comparison of Different Types of Adders

ISSN: 2278-0181

#### IX. CONCLUSION

Adders are used for arithmetic calculations. Different types of adders like RCA, CSA, CLA, CSKA, CSVA and PPA are available. The performance of these adders can be measured in terms of parameters like Area, Speed, Delay and Cost. The detailed literature survey of adders has been done in this paper. And also, they are compared with each other to choose a specific one for a particular requirement. According to our survey we found that PPA is the better adder in performance compared to other adders. We can always have trade-off between few performance factors when we select specific adder as per the needs. The adder can also be implemented using any of CAD tools to observe and analyse different factors like power consumption, fan in, fan out, wiring tracks and logic levels.

### REFERENCES

- [1] Suhel Ranjan Mondal, Monalisa Bhowmik, Santanu Maity, Razia Sultana, "Comparative Analysis and Study on 4-bit RCA and CSK using CMOS Logic", International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-4 Issue-6, January 2015.

- [2] Rajesh, D & Sowmya, S & Subashini, M & Suryaprabha, P & Gowthaman, Naveen Balaji & Suman, Gautami. (2018). Investigations of Carry Look Ahead Adder at V DD =1.0V at 65nm CMOS Technology for High Speed and Low Power Applications.

- International Journal of Latest Research in Science and Technology. 7.

- [3] B.Gopinath1, N.Sangeetha2, S.Jenifer nancy3 and T.Umarani4 1Asst. Professor Dr. SJS Paul Memorial College of Engineering & Technology, Puducherry. 234Student Dr. SJS Paul Memorial College of Engineering & Technology, Pondicherry. "Design and Implementation of High Speed Carry Select Adder". International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 IJERTV4IS020383 www.ijert.org (This work is licensed under a Creative Commons Attribution 4.0 International License.) Vol. 4 Issue 02, February-2015.

- [4] P.Lakshmi Priyanka1 P.G. Student Dept. of ECE AITS Kadapa, India, A.Maheswar Reddy2 Dept. of ECE AITS Kadapa, India M.V.Subbaiah3 Dept. of ECE AITS Kadapa, India K.md.Haneef4 Dept. of ECE AITS Kadapa, India, S.Saleem5 Dept. of ECE AITS Kadapa, India. "Carry Skip Adder Using Carry Save Adder Logic". SSRG International Journal of Electronics and Communication Engineering (SSRG\_IJECE) – Special Issue ICITSET Sep 2018.

- [5] Junhyung Um, & Taewhan Kim. (n.d.). Utilization of carry-save-adders in arithmetic optimization. Twelfth Annual IEEE International ASIC/SOC Conference (Cat. No.99TH8454). doi:10.1109/asic.1999.806498.

- [6] Sung-Mo(Steve)Kang Korea Advanced Institute of Science and Technology University of California at Santa Cruz, Yusuf Leblebici Swiss Federal Institute of Technology-Lausanne, Chulwoo Kim Korea University-Seoul. "CMOS Digital Integrated Circuits Analysis and Design". McGraw Hill Education (India) Private Limited

- [7] Er. Aradhana Raju, Richi Patnaik, Ritto Kurian Babu, Purabi Mahato Department of ECE, Silicon Institute of Technology, Bhubaneswar, Khurda (Dist), Odisha, Parallel Prefix Adders- A Comparative Study For Fastest Response.