### **NCICCT-2015 Conference Proceedings**

# A Robust and Reconfigurable Multi-Mode Power **Gating System to Reduce Static Power Loss**

D. Suganya ECE Department, JCET Trichy, India

S. Syedshaffi Assistant professor, ECE Department, JCET Trichy, India

Abstract - Multithreshold Complementary Metal Oxide Semiconductor (MTCMOS) is very effective for reducing standby leakage power during long periods of inactivity. A power-gating scheme was used to provide multiple power off modes and reduce the leakage power during short periods of inactivity. This scheme can suffer from high sensitivity to process variations of logic. We propose a new power-gating technique that is tolerant to process variations and scalable to more than two intermediate power-off modes. The Tanner Electronic Design Automation (EDA) tool is used to design the schematic for multiplier with power gating system.It is very simple and all-digital, and it is minimally sized. It consumes low static power. It has high tolerance to manufacturing process variations. The proposed design requires less design effort and offers greater power reduction and smaller area cost than the previous method. In addition, it will be combined with existing method to offer further static power reduction. The schematic design is to generate the waveform and produce some power consumption. A reconfigurable version of this method can be used to increase the manufacturability and robustness of the proposed design in technologies with larger process variations.

Key words—Leakage power, MMPS, power consumption reduction, Tanner EDA, process variation.

# **I.INTRODUCTION**

Multi-threshold CMOS is a budding know-how that provide high concert and low command function by utilizing both high and low Vt transistors. By low Vt transistors in the indication lane, the provide voltage can be lowered to diminish switching power indulgence. By dipping V<sub>dd</sub>, the switching influence can be condensed quadratic ally, but as V<sub>t</sub> decreases to continue routine, the sub entrance seepage contemporary will increase exponentially. For ruthless scaling, the better outflow supremacy can really direct the switching power. Recently, several dealer goods in the low command fixed liberty offer power-gating bear in the appearance of "sleep" modes, typically software run. One of numerous supercomputer cores, in such as arrangement, runs at the greatest in use regularity and the other mainframe cores can be power-gated off when the working classification detects a elongated inoperative loop. The destructive power-saving line of attack above, but, has the follow probable harms. The scaling of development technologies to nanometer

administration has resulted in a rapid make bigger in

seepage power rakishness. Hence, it has befallen

enormously significant to extend devise techniques to

diminish fixed clout debauchery all through periods of

immobility. The power lessening must be achieved devoid of trading-off show which makes it harder to reduce leakage during normal operation. On the other hand, there are several techniques for reducing leakage power in sleep or standby mode. This device is turned-off in the sleep mode to cut-off the leakage path. It has been shown that this technique provides asubstantial reduction in leakage at a minimal impact on performance.

#### II. RELATED WORK

As chip density increases relentless along Moore law, power consumption is emerging as a major burden for contemporary systems [1], To reduce the dynamic power, systems-on-chip (SoCs) are partitioned into voltage islands with separate supply rail and unique power characteristics

Many techniques have been presented in the literature for reducing static power. One common approach is to synthesize the circuit using dual-V<sub>t</sub>libraries [6]. High-V<sub>t</sub>cells reduce the leakage current at the expense of reduced performance; in order to reduce static power, it controls the input vector and the internal state of the circuit during periods of inactivity [7]–[11].

Various techniques reduce peak rush current [22]-[25]. A more aggressive technique is the use of high- V<sub>t</sub>power switches between the circuit and the power supply or the ground rail [6], [12]-[20]. These switches are turned off during the idle mode, thereby suppressing leakage current. A major problem is the large current rush during the reactivation of the core, which causes power supply and ground bounce [21], [22].

The authors of [28] proposed a structure with one intermediate power-off mode, which reduces the wake-up time at the expense of reduced leakage current suppression. Similar structures were proposed in [27] and [29]. The authors of [26] extended this tradeoff between wake-up overhead and leakage power savings into multiple poweroff modes. Using these techniques, instead of consuming power by remaining in the active mode during the short periods of inactivity, the circuit is put into an appropriate power-off mode (i.e., low-power state), which is determined by both the wake-up time and the length of the idle period.

In this work, we present an effective and robust multimode power-gating architecture that has none of the above drawbacks of the architecture proposed in [26]. The proposed structure requires minimal design effort since it is very simple, and with no analog components. It is

1

ISSN: 2278-0181

considerably smaller than the architecture proposed in [26] and offers greater power savings for similar wake-up times. The proposed architecture is also more tolerant to processvariations than [26], thus its operation is more predictable. Finally, a reconfigurable version of the proposed architecture is also proposed, which can tolerate even greater process variations, enabling thus the utilization of the proposed architecture for newer technologies.

#### III. PROBLEM FORMULATION

The offered makeup requires least design endeavor seeing as it is exceedingly undemanding, and among no analog machinery. It is very much slighter than the planning accessible and offers superior control reserves for like awaken period. The projected construction is also added liberal to course variations; thus its action is more conventional. In vacant means four methods are there. In this methods are

- Active Mode

- Snore Mode

- Dream Mode

- Sleep Mode

# A.ACTIVE MODE

• Transistors MP, M0, M1 are ON.

# B.SNORE MODE

• Transistors MP, M0, and M1 are OFF.

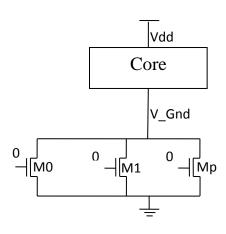

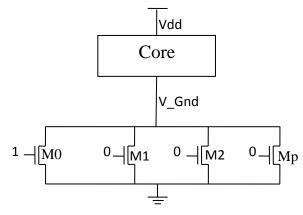

Fig.1 Snore mode

- The escape topical of the nucleus I Lcore, is the same to the amassed flight modern elegant throughout transistors M0, M1, MP (I Lcore = I LM0 + I LM1 + I LMP), which is very minute.

- The power plane at V\_GND is secure to V<sub>dd</sub> and the course consumes a small total of vigor, but the wake-up instance is elevated.

#### C.DREAM MODE

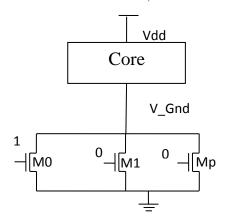

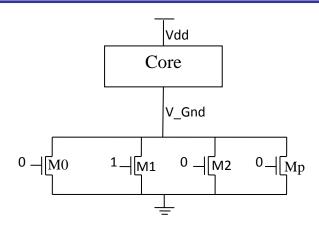

- Transistor M0 is on and transistors MP and M1 are OFF.

- In this holder, the contemporary smooth during transistor M0 increases as M0 is on (IM0 > I LM0).

- The exact value of IM0 depends on the size of transistor M0, VV\_GND < V<sub>dd</sub>. Thus the static power consumed by the core is higher compared to the snore mode, but the wake-up time is less.

Fig.2 Dream mode

#### D.SLEEP MODE

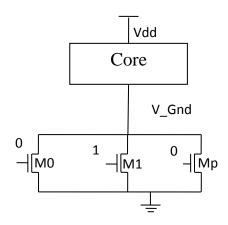

Fig.3 Sleep mode

- Transistor M1 is on, and MP, M0 are OFF.

- The transistor M1 has larger aspect ratio than M0 (WM1/LM1 > WM0/LM0), the aggregate current flowing through M0, M1, and MP increases even more when M1 is on.

- Consequently, the voltage level at the virtual ground node is further reduced compared to the dream mode and thus the wake-up time decreases at the expense of increased power consumption.

## IV. SYSTEM DESCRIPTION

Power gating is a technique used in integrated circuit design to reduce power consumption, by shutting off

**NCICCT-2015 Conference Proceedings**

the current to blocks of the circuit that are not in use. In addition to reducing stand-by or leakage power, power gating has the benefit of enabling I<sub>ddq</sub> testing.

#### A.MULTIMODE POWERGATING SYSTEM

The offered makeup requires least design endeavor seeing as it is exceedingly undemanding, and among no analog machinery. It is very much slighter than the planning accessible and offers superior control reserves for like awaken period.

The projected construction is also added liberal to course variations; thus its action is more conventional. In vacant means four methods are there. In this methods are

- Active Mode

- Snore Mode

- Dream Mode

- Sleep Mode

- Nap Mode

#### **B.ACTIVE MODE**

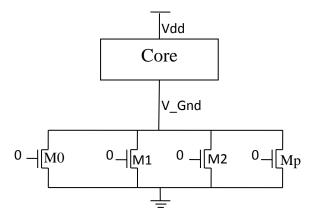

Transistors MP, M0, M1 and M2 are ON.

#### C.SNORE MODE

- The virtual ground rail (V\_GND) charges to a voltage level VSnore close to the power-supply.

- The leakage currents of the transistors of the circuit are suppressed. In this mode the leakage current of the core, ILcore, is equal to the aggregate leakage current flowing through transistors M0, M1, M2, MP (ILcore = ILM0 + ILM1 + ILM2 + ILMP), which is very small.

- Thus, the voltage level VSnore at virtual ground rail VV\_GND approaches V<sub>dd</sub> and the circuit consumes a negligible amount of energy.

In order to restore the voltage of the virtual ground rail to its nominal value when the circuit N transitions from the power-off mode to the active mode, the parasitic capacitance at the V GND node has to be completely discharged through the power switch MP which is turnedon again.

Fig.4 Snore mode

However, the aggregate size of the transistors comprising the power switch MP is relatively small compared to the size of the core and thus it cannot quickly discharge the V GND node. Thus the wake-up time can be long relative to circuit clock period, and MP cannot be turned-off during short periods of inactivity.

# D.DREAM MODE

- The current flowing through transistor M0 increases compared to the snore mode because M0 is on (IM0 > ILM0).

- The exact value of IMO depends on the size of transistor M0, and it sets the V GND node at a voltage level VDream which is lower than that of the snore mode (VDream < VSnore).

- Thus the static power consumed by the core increases compared to the snore mode, but the wake-up time drops.

Fig.5 Dream mode

#### E.SLEEP MODE

- The sleep mode is implemented by decreasing the voltage level at the virtual ground node.

- This is achieved by using transistor M1 which has larger aspect ratio than M0 (WM1/LM1 > WM0/LM0).

- When only M1 is turned-on the aggregate current flowing through M0, M1, and MP increases even more and the voltage level VSleep at the virtual ground node is further reduced compared to the dream mode (VSleep < VDream < VSnore).

ISSN: 2278-0181

Fig.6 Sleep mode

The wakeup time decreases at the expense of increased static power consumption, which however, remains much lower than the static power of the active mode.

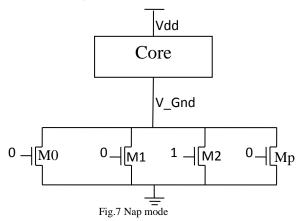

#### F.NAP MODE

The "nap" mode is implemented by further increasing the aspect ratio of the respective power switch (i.e., WM2/LM2 > WM1/LM1 > WM0/LM0).

- In nap mode the voltage level at V\_GND node is set at VNap, where VNap < VSleep < VDream <

- The static power consumption increases and the wake-up time reduce even more.

# V. RESULT AND DISCUSSION

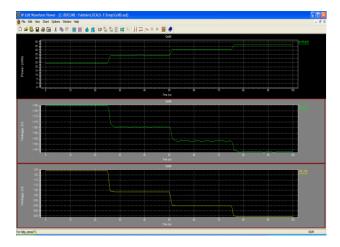

The system can be implemented using Tanner EDA tool. A 4×4 multiplier circuit can be used as a logic circuit and ground of logic can be connected on the Power switches. Various mode of operation can be simulated and its ground voltage can be calculated.

Table (1):Power consumption for various modes

| Mode       | Ground voltage(v) | Power<br>(mW) |

|------------|-------------------|---------------|

| Snore Mode | 1.85              | 25            |

| Sleep Mode | 1.65              | 33            |

| Nap Mode   | 0.95              | 37            |

| Dream Mode | 0.45              | 44            |

Fig.8 power Gating system Output

In future we have to use multimode power gating system to reduce Dynamic power loss and also reduce the Delay. Otherwise, A new low voltage charge pump is developed to help start up a step-up converter in energy harvesting applications.

# VI.CONCLUSION

Amultimode power-gating system is used to reduce the static power loss.In this scheme that provides multiple power-off modes. The proposed design offered the advantage of simplicity and required minimum design effort. Extensive simulation results showed that, in contrast to a recent power-gating method, the proposed design is robust to process variations and it is scalable to more than two intermediate power offmodes. Moreover, it requires significantly less area and consumes much less power than the previous design.

# REFERENCE

- Semiconductor Industry Association. [Online] Available: http://www.itrs.net/Links/2007ITRS/Home2007.h

- [2] D. Lackey, P. Zuchowski, T. Bednar, D. Stout, S. Gould, and J. Cohn, "Managing power and performance for system-on-chip designs using voltage islands," in *Proc. IEEE/ACM Int. Conf.* Comput. Aided Design, Nov. 2002, pp. 195-202.

- [3] R. Puri, D. Kung, and L. Stok, "Minimizing power with flexible voltage islands," in Proc. IEEE Int. Symp. Circuits Syst., May 2005, pp. 21-24.

- R. Puri, L. Stok, J. Cohn, D. Kung, D. Pan, D. Sylvester, A. Srivastava, and S. Kulkarni, "Pushing ASIC performance in a power envelope," in Proc. Design Autom. Conf., Jun. 2003, pp. 788-793.

ISSN: 2278-0181

- [5] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305-327, Feb. 2003.

- S. Idgunji, "Case study of a low power MTCMOS based ARM926 SoC: Design, analysis and test challenges," in Proc. IEEE Int. Test Conf., Oct. 2007, pp. 1-10.

- A. Abdollahi, F. Fallah, and M. Pedram, "Leakage current reduction in CMOS VLSI circuits by input vector control," IEEE Trans. Very LargeScale Integr. (VLSI) Syst. vol. 12, no. 2, pp. 140-154, Feb.

- Y. Alkabani, T. Massey, F. Koushanfar, and M. Potkonjak, "Input vector control for post-silicon leakage current minimization in the presence of manufacturing variability," in Proc. 45th ACM/IEEE Design Autom. Conf., Jun. 2008, pp. 606–609.

- K. Kim, Y.-B. Kim, M. Choi, and N. Park, "Leakage minimization technique for nanoscale CMOS VLSI," IEEE Des. Test Comput., vol. 24, no. 4, pp. 322-330, Jul. 2007.

- [10] S. Mukhopadhyay, C. Neau, R. Cakici, A. Agarwal, C. Kim, and K. Roy, "Gate leakage reduction for scaled devices using transistor stacking," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 11, no. 4, pp. 716-730, Aug. 2003.

- [11] H. Suzuki, W. Jeong, and K. Roy, "Low-power carry-select adder using adaptive supply voltage based on input vector patterns," in Proc. Int.Symp. Low Power Electron. Design Conf., Aug. 2004, pp.

- [12] M. Anis, S. Areibi, and M. Elmasry, "Design and optimization of multithreshold CMOS (MTCMOS) circuits," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 22, no. 10, pp. 1324-1342, Oct. 2003.

- [13] M. Anis, S. Areibi, M. Mahmoud, and M. Elmasry, "Dynamic and leakage power reduction in MTCMOS circuits using an automated efficient gate clustering technique," in Proc. 39th Design Autom. Conf., Jun. 2002, pp. 480-485.

- [14] M. Anis and M. Elmasry, Multi-Threshold CMOS Digital Circuits— Managing Leakage Power. Norwell, MA: Kluwer, 2003.

- [15] J. Kao and A. Chandrakasan, "MTCMOS sequential circuits," in Proc. 27th Eur. Solid-State Circuits Conf., Sep. 2001, pp. 317–320.

- [16] J. Kao, S. Narendra, and A. Chandrakasan, "MTCMOS hierarchical sizing based on mutual exclusive discharge patterns," in Proc. DesignAutom. Conf., Jun. 1998, pp. 495-500.

- [17] H. Kawaguchi, K. Nose, and T. Sakurai, "A super cut-off CMOS (SCCMOS) scheme for 0.5 V supply voltage with picoampere standby current," IEEE J. Solid-State Circuits., vol. 35, no. 10, pp. 1498-1501, Oct. 2000.

- [18] S. Kosonocky, M. Irnmediato, P. Cottrell, T. Hook, R. Mann, and J. Brown, "Enhanced multi-threshold (MTCMOS) circuits using variable well bias," in Proc. Int. Symp. Low Power Electron. Design Conf., 2001, pp. 165-169.

- S. Mutoh, T. Douseki, Y. Matsuya, T. Aoki, S. Shigematsu, and J. Yamada, "1 V power supply high-speed digital circuit technology with multithreshold-voltage CMOS," *IEEE J. Solid-State Circuits*, vol. 30, no. 8, pp. 847-854, Aug. 1995.

- [20] S. Shigematsu, S. Mutoh, Y. Matsuya, Y. Tanabe, and J. Yamada, "A 1 V high-speed MTCMOS circuit scheme for power-down application circuits," IEEE J. Solid-State Circuits, vol. 32, no. 6, pp. 861-869, Jun. 1997.

- [21] P. Heydari and M. Pedram, "Ground bounce in digital VLSI circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 11, no. 2, pp. 180-193, Apr. 2003.

- S. Kim, S. Kosonocky, and D. Knebel, "Understanding and minimizing ground bounce during mode transition of power gating structures," in Proc. Int. Symp. Low Power Electron. Design, Aug. 2003, pp. 22-25.

- [23] A. Calimera, L. Benini, A. Macii, E. Macii, and M. Poncino, "Design of a flexible reactivation cell for safe power-mode transition in powergated circuits," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 56, no. 9, pp. 1979-1993, Sep. 2009.

- [24] S. Henzler, G. Georgakos, J. Berthold, and M. Eireiner, "Activation technique for sleep-transistor circuits for reduced power supply noise," in Proc. 32nd Eur. Solid-State Circuits Conf., Sep. 2006, pp. 102-105.

- [25] K. Kim, H. Nan, and K. Choi, "Ultralow-voltage power gating structure using low threshold voltage," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 56, no. 12, pp. 926-930, Dec. 2009.

- [26] [42] H. Singh, K. Agarwal, D. Sylvester, and K. Nowka, "Enhanced leakage reduction techniques using intermediate strength power gating," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 11, pp. 1215-1224, Nov. 2007

- [27] [43]M. H. Chowdhury, J. Gjanci, and P. Khaled, "Innovative power gating for leakage reduction," in *Proc. IEEE Int. Symp. Circuits* Syst. Conf., May 2008, pp. 1568-1571.

- [28] S. Kim, S. Kosonocky, D. Knebel, and K. Stawiasz, "Experimental measurement of a novel power gating structure with intermediate power saving mode," in Proc. Int. Symp. Low Power Electron. Design, Aug. 2004, pp. 20-25.

- [29] E. Pakbaznia and M. Pedram, "Design and application of multimodal power gating structures," in Proc. Qual. Electron. Design Conf., Mar. 2009, pp. 120–126.

[30] H. Jiao and V. Kursun, "Ground bouncing noise suppression

- techniques for data preserving sequential MTCMOS circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 5, pp. 763-773,May 2011.

- [31] H. Jiao and V. Kursun, "Threshold voltage tuning for faster activationwith lower noise in tri-mode MTCMOS circuits," *IEEE* Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 4, pp. 741-745, Apr. 2012.

- [32] S. Kim, C. J. Choi, D.-K. Jeong, S. Kosonocky, and S. B. Park, "Reducingground-bounce noise and stabilizing the data-retention voltage ofpower-gating structures," IEEE Trans. Electron. Devices, vol. 55, no. 1,pp. 197–205, Jan. 2008.

- [33] S. Kim, S. Kosonocky, D. Knebel, K. Stawiasz, and M. Papaefthymiou,"A multi-mode power gating structure for lowvoltage deep-submicronCMOS ICs," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 7,pp. 586–590, Jul. 2007.

- [34] E. Pakbaznia and M. Pedram, "Design of a tri-modal multithresholdCMOS switch with application to data retentive power gating," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2,pp. 380-385, Feb. 2012.

- [35] R. Singh, J.-K. Woo, H. Lee, S. Y. Kim, and S. Kim, "Power-gating noiseminimization by three-step wake-up partitioning," IEEE Trans. CircuitsSyst. I, Reg. Papers, vol. 59, no. 4, pp. 749–762, Apr. 2012.

- [36] R. Singh, A. Kim, S. Kim, and S. Kim, "A three-step powergatingturn-on technique for controlling ground bounce noise,' Proc.ACM/IEEE Int. Symp. Low-Power Electron. Design Conf., Aug. 2010,pp. 171-176.

- [37] K.-S. Min, H.-D. Choi, H.-Y. Choi, H. Kawaguchi, and T. Sakurai,"Leakage-suppressed clock-gating circuit with zigzag super cut-offCMOS (ZSCCMOS) for leakage-dominant sub-70-nm and sub-1-v-vDDLSIs," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 4,pp. 430-435, Apr. 2006.

- [38] K.-I. Kawasaki, T. Shiota, K. Nakayama, and A. Inoue, "A sub-s wakeuptime power gating technique with bypass power line for rush currentsupport," IEEE J. Solid-State Circuits., vol. 44, no. 4, pp. 1178-1183, Apr. 2009.

- [39] C. Akl and M. Bayoumi, "Reducing wakeup latency and energyof MTCMOS circuits via keeper insertion," in Proc. ACM/IEEEInt. Symp. Low Power Electron. Design Conf., Aug. 2008,pp. 69-74.

- [40] S. Kim, S. Kosonocky, D. Knebel, and K. Stawiasz, "Experimentalmeasurement of a novel power gating structure with intermediatepower saving mode," in Proc. Int. Symp. Low Power Electron. Design, Aug. 2004, pp. 20–25.

[41] E. Pakbaznia and M. Pedram, "Design and application of

- multimodalpower gating structures," in Proc. Qual. Electron. Design Conf., Mar. 2009, pp. 120-126.

- [42] H. Singh, K. Agarwal, D. Sylvester, and K. Nowka, "Enhanced leakagereduction techniques using intermediate strength power gating," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 11,pp. 1215-1224, Nov. 2007.

- [43] Z. Zhang, X. Kavousianos, K. Chakrabarty, and Y. Tsiatouhas, "A robustand reconfigurable multi-mode power gating architecture," in Proc. 24th Int. Conf. VLSI Design, 2011, pp. 280-285.

- [44] J. M. Rabaey, A. Chandrakasan, and B. Nicolic, Digital IntegratedCircuits A Design Perspective. Englewood Cliffs, NJ: Prentice Hall, Jan. 2003.

- [45] S. Henzler, T. Nirschl, S. Skiathitis, J. Berthold, J. Fischer, P. Teichmann, F. Bauer, G. Georgakos, and D. Schmitt-Landsiedel, "Sleeptransistor circuits for fine-grained power switch-off with short powerdowntimes," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2005,pp. 302-600.