# *A novel method to improve THD of multilevel inverter by multisampling*

SANJU. K.SURESH

PG Student, ECE Department

Hindustan College of Engineering and technology

Coimbatore, India

Sanju254@gmail.com

M.P.VISWANATHAN

Assistant Professor, EEE Department

Hindustan College of Engineering and technology

Coimbatore, India

viswaveena@gmail.com

**Abstract**—This paper introduces multilevel inverters. Inverters can be broadly classified into single level inverter and multilevel inverter. Multilevel inverters when compared to single level inverters have advantages like minimum harmonic distortion and reduced EMI generation it can also operate on several voltage levels. In the existing system 5 level inverter is used. It reduces THD compared to the conventional switching system. In the proposed system seven level inverter by multi sampling technique is being implemented. Proposed method is implemented using SIMULINK. By using the multi sampling technique system performance can be increased as well as the harmonics can be reduced. Conventional digital control power converters usually use a technique known as uniform sampling.

**Index Terms**—, Digital control, control gain, multisampling, multilevel inverters, electro magnetic interference.

## I. INTRODUCTION

Various industrial applications have begun to require higher power apparatus in the recent times. Mainly medium voltage motor drives and utility applications requires medium voltage and very high power level. For a medium voltage grid, it is difficult to connect only one power semiconductor switch. Hence, a multilevel power converter structure has been introduced as an alternative in high and medium power voltage applications. A multilevel converter not only helps to achieve high power ratings, but it also enables the use of renewable sources of energy. Renewable sources of energy such as photovoltaic cells, wind, and fuel cells can also be easily interfaced to a multilevel converter system for very high power applications.

The concept of multilevel converters have been known since 1975 . The term multilevel began with the three level converters. Further, several multilevel converter topologies have been proposed. But the most basic concept of a multilevel converter to achieve high power is to use a series of power semiconductor switches having several low voltage dc sources so as to perform the power conversion by synthesizing a voltage waveform which is a staircase waveform here. We can use capacitors, batteries, and also renewable energy voltage sources as multiple dc voltage sources. Commutation of the power switches combines these dc sources in order to attain high voltage at the output, yet, the rated voltage of the

power semiconductor switches counts only upon the rating of the dc voltage sources to which they are being connected.

A multilevel converter has several advantages over a conventional two-level converter that uses high switching frequency pulse width modulation (PWM). The attractive features of a multilevel converter can be briefly summarized as follows.

**Staircase waveform quality:** Multilevel converters not only can generate the output voltages with very less distortion, but it also can bring down the dv/dt stresses; therefore electromagnetic compatibility (EMC) problems can be reduced.

**Common-mode voltage (CM):** Multilevel converters produces small CM voltage, hence the stress in the bearings of a motor which is connected to a multilevel motor drive can be reduced. Further, CM voltage can be rejected by using advanced modulation strategies.

**Input current:** Multilevel converters can draw input current with very less distortion.

**Switching frequency:** Multilevel converters can operate both at fundamental switching and high switching frequency PWM. It should be also noted that lowering switching frequency usually means higher efficiency and lower switching loss.

Unluckily, multilevel converters also have some disadvantages. One peculiar disadvantage is larger the number of power semiconductor switches are required. Though lower voltage rated switches can be applied in a multilevel converter, here each switch needs a concerned gate drive circuit. This can cause the overall system to be more and more complex and expensive.

Various multilevel converter topologies have been suggested during the last two decades. Modern day researches has engaged unique modulation schemes and novel converter topologies.

## II. MULTISAMPLED MULTILEVEL INVERTERS

To demonstrate the improved control performance as a result of the multisampled multilevel inverter, this section provides a detailed analysis of the system's operation in contrast to the bipolar switched inverter. A system comprised of two cascaded H-bridges inverters and modulated by four phase-shifted triangle carriers with octuple-sampling frequency is modeled. The analysis is undertaken to assess the

606

Sanju. K.Suresh, M.P.Viswanathan

performance advantages of the multisampled multilevel inverter.

#### A. System Configuration

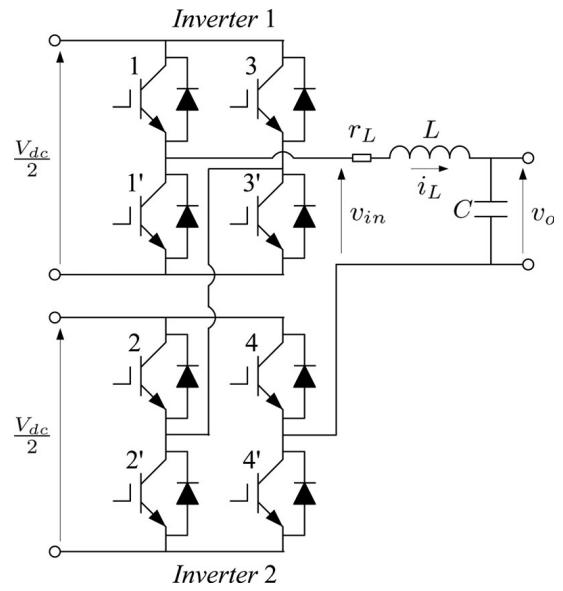

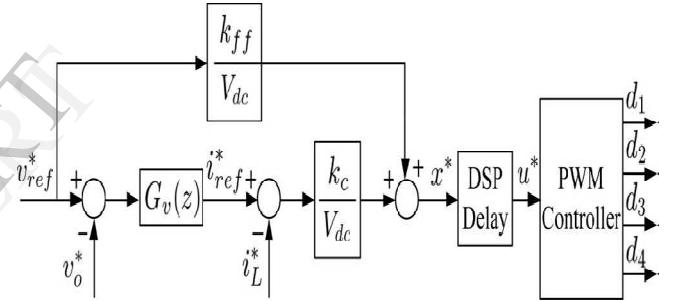

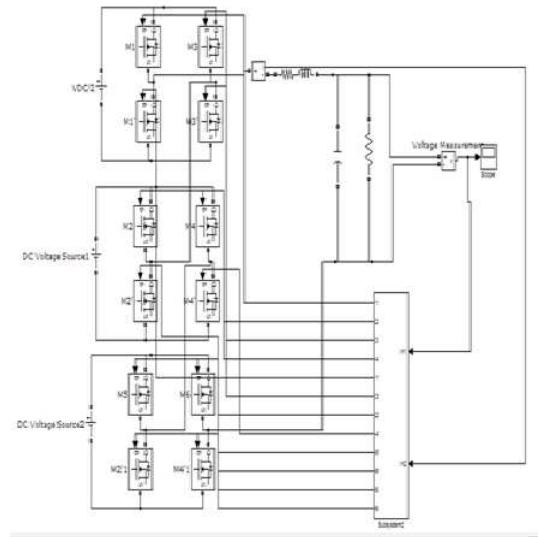

The power circuit of a multilevel inverter with two cascaded H-bridges is shown in Fig.1. Compared to the single H-bridge inverter, the dc voltage for each bridge is halved. The drive signals for the upper and lower switches in each leg are complementary. Therefore, four independent drive signals are generated from the digital controller which block diagram is shown in Fig.2.

#### B. Phase-Shifted PWM

Two typical modulation strategies are usually used for multilevel inverters. The level-shifted modulation method requires the same switching frequency as the filter current ripple frequency. To achieve higher ripple frequency than switching frequency, the phase-shifted PWM can be employed for the multilevel inverters. This modulation method is characterized by its capability of improving the control performance of the filter voltage and current [24]. Since the filter input voltage frequency is increased as multiples of the switching frequency, achieving an enhanced dynamic performance becomes feasible. However, a proper model for the digital PWM which can be used to design the controller has not been proposed to date.

### III. SIMULATION MODEL

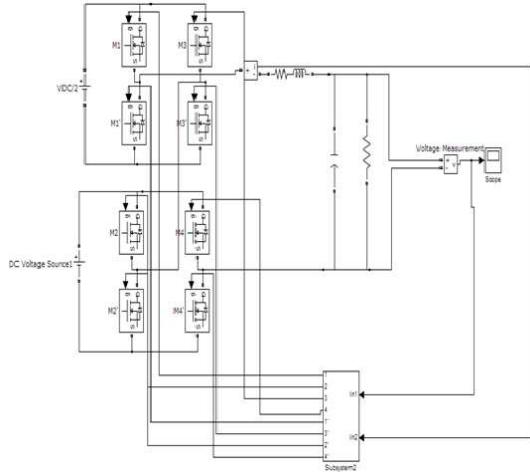

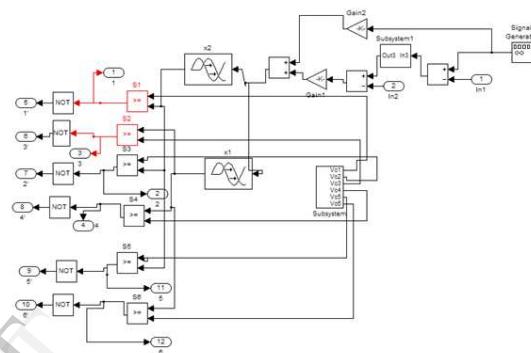

Here we are comparing a 5 level multi level inverter with a 7 level multilevel inverter structure. Here bridge is formed by connecting four MOSFETs and this is called an inverter. Here in the Fig.3. Block diagram of the existing system is seen. Here we take two inverters And we are using a single phase inverter. Here we use cascaded topology for connecting the inverters. Here we use LC filter circuit. We use inductor in series for current measurement and capacitor in parallel for voltage measurement.

Fig.1. Five-level H-bridge inverter.

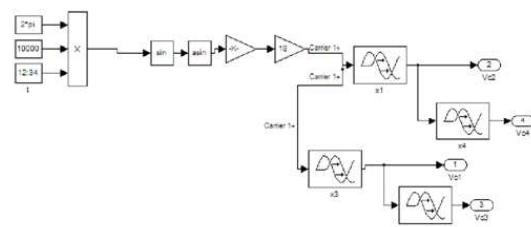

Fig.2. Digital controller of the five-level H-bridge inverter.

Fig.3. Block diagram of 5 level inverter.

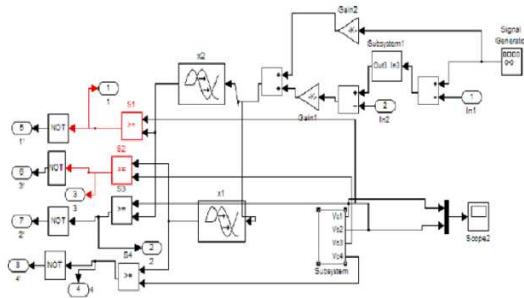

Fig.4. Subsystem of 5 level inverter.

Fig.4. and Fig.5. shows the block diagram of the subsystem of the existing system which uses five level of inverters. Which is implemented using two inverters.

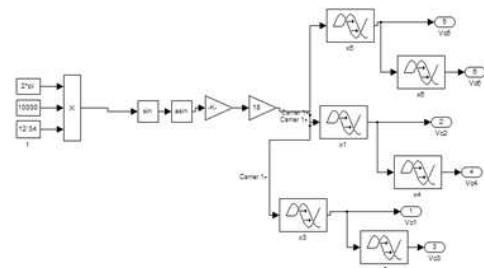

Fig.6. Block diagram of the 7 level inverter.

Fig.6. shows the block diagram of the proposed system. Here six MOSFETs are connected to form three inverters and here a seven level inverter is considered. Where as in the existing system four MOSFETs are connected together to form two inverters. Here also we use LC filter circuit with resistive load connected to it. Inductor in series is used for current measurement and capacitor in parallel for voltage measurement.

Fig.5. Subsystem of 5 level inverter.

Fig.7. Subsystem of the 7 level inverter.

In the existing system we use four delays to generate the output. But in the proposed system we use six delays for generating the output. Advantage of using more delay is that the overall THD decreases as well as the inverter performance increases.

Fig.8. Subsystem of the 7 level inverter.

#### IV.RESULTS AND DISCUSSION

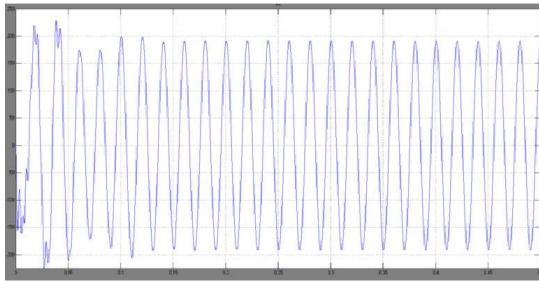

Fig.9. Output voltage waveform of the 5 level inverter.

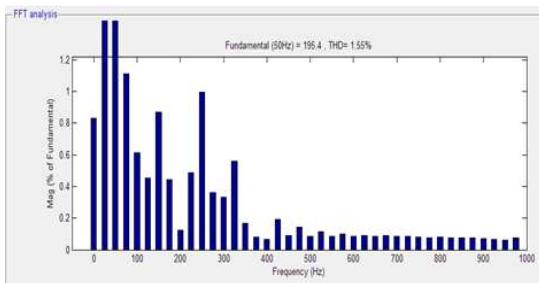

Fig.9. shows the output voltage waveform. Fig.10. shows the THD waveform of the existing system. Here we observe the THD output to be 1.55. It is expressed in percentage. Existing system is an inverter with 5 levels. For an efficient inverter the THD must be minimized so in the proposed system we go for a seven level inverter.

Fig.10. THD waveform of the 5 level inverter.

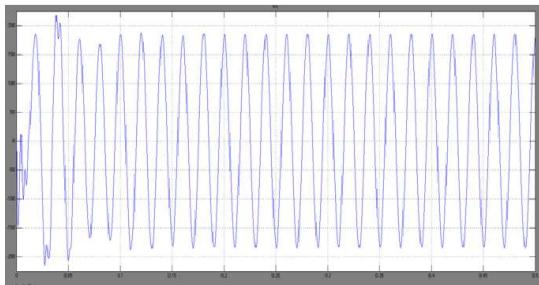

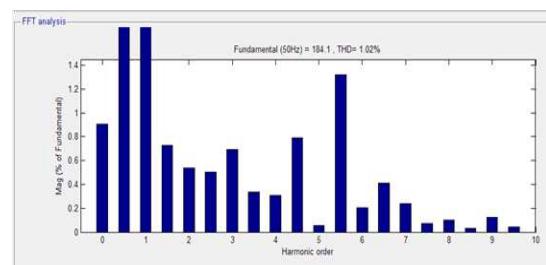

Here the Fig.11. shows the output voltage waveform for the seven level inverter. Also in the Fig.12. it shows the THD waveform for the proposed system. Since we use a seven level inverter system and six delays, the overall THD gets reduced.

Fig.11. Output voltage waveform of the 7 level inverter.

Fig.12. THD waveform of the 7 level inverter.

## V.CONCLUSION

In the existing technique a five level inverter is implemented which reduced the THD compared to the conventional switching system. In the proposed system level of inverter is increased to seven by the multisampling technique which further reduced THD. Thus increasing the inverter performance. Using multi sampling technique harmonics is also reduced. So by using multisampling technique harmonics is reduced in a very efficient way. From the result analysis it is observed that when five level inverter is used, the THD is 1.55 where when we use seven level inverter THD has been reduced to 1.02.

## REFERENCES

- [1] D. M. Van de Sype, K. De Gusseme, A. P. Van den Bossche, and J. A. Melkebeek, "A sampling algorithm for digitally controlled boostPFC converters," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 649–657, May 2004.

- [2] P. Mattavelli, G. Spiazzini, and P. Tenti, "Predictive digital control of powerfactor preregulators with input voltage estimation using disturbance observers," *IEEE Trans. Power Electron.*, vol. 20, no. 1, pp. 140–147, Jan. 2005.

- [3] W. Stefanutti, P. Mattavelli, G. Spiazzini, and P. Tenti, "Digital control of single-phase power factor preregulators based on current and voltagesensing at switch terminals," *IEEE Trans. Power Electron.*, vol. 21, no. 5, pp. 1356–1363, Sep. 2006.

- [4] P. Mattavelli, F. Polo, F. Dal Lago, and S. Saggini, "Analysis of controldelay reduction for the improvement of UPS voltage-loop bandwidth," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2903–2911, Aug. 2008.

- [5] H. Fujita, "A single-phase active filter using an H-bridge PWM converter with a sampling frequency quadruple of the switching frequency," *IEEE Trans. Power Electron.*, vol. 24, no. 4, pp. 934–941, Apr. 2009.

- [6] M. Hartmann, S. D. Round, H. Ertl, and J. W. Kolar, "Digital currentcontroller for a 1 MHz, 10 kW three-phase VIENNA rectifier," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2496–2508, Nov. 2009.

- [7] L. Corradini, P. Mattavelli, E. Tedeschi, and D. Trevisan, "High-bandwidth multisampled digitally controlled DC-DC converters using ripple compensation," *IEEE Trans. Ind. Electron.*, vol. 55, no. 4, pp. 1501–1508, Apr. 2008.

- [8] L. Corradini and P. Mattavelli, "Modeling of multisampled pulse widthmodulators for digitally controlled DC-DC converters," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1839–1847, Jul. 2008.

- [9] L. Corradini, P. Mattavelli, and S. Saggini, "Elimination of samplinginduceddead bands in multiple-sampled pulsewidth modulators for DCDC converters," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2661–2665, Nov. 2009.

- [10] L. Corradini, W. Stefanutti, and P. Mattavelli, "Analysis of multisampled current control for active filters," *IEEE Trans. Ind. Appl.*, vol. 44, no. 6, pp. 1785–1794, Nov./Dec. 2008.

- [11] L. Tolbert and T. Habetler, "Novel multilevel inverter carrier-based PWM method," *IEEE Trans. Ind. Appl.*, vol. 35, no. 5, pp. 1098–1107, Sep./Oct. 1999.

- [12] N. Celanovic and D. Boroyevich, "A fast space-vector modulation algorithm for multilevel three-phase converters," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 637–641, Mar./Apr. 2001.

- [13] R. Teodorescu, F. Blaabjerg, J. Pedersen, E. Cengelci, and P. Enjeti, "Multilevel inverter by cascading industrial VSI," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 832–838, Aug. 2002.

- [14] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [15] G. Carrara, S. Gardella, M. Marchesoni, R. Salutari, and G. Scututto, "A new multilevel PWM method: A theoretical analysis," *IEEE Trans. Power Electron.*, vol. 7, no. 3, pp. 497–505, Jul. 1992.

- [16] D. Holmes and B. McGrath, "Opportunities for harmonic cancellation with carrier-based PWM for a two-level and multilevel cascaded inverters," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 574–582, Mar./Apr. 2001.

IJERT