International Journal of Engineering Research & Technology (IJERT) Vol. 12 Issue 04, April-2023

# A Comparison of Nine Level Cascaded H-Bridge Multilevel Inverter with Five Level Cascaded H **Bridge Multilevel Inverter**

Divya Subramanian Department of Electrical and Electronics Engineering Nirmala Institute of Technology Thrissur India

Abstract—The multilevel inverter utilization has been increased since the last decade. These new types of inverters are suitable in various high voltage & high-power application due to their ability to synthesize waveforms with better harmonic spectrum and faithful output. This paper presents a comparison of nine-level cascaded H-bridge multilevel inverter with five-level cascaded Hbridge multilevel inverter. Multicarrier phase-shifted pulse-width modulation method is used to achieve balanced power distribution among the power cells. The analysis of the output voltage harmonics is carried out. From the results, the nine-level cascaded H-bridge multilevel inverter provides higher output quality with relatively lower power loss as compared to the five-level cascaded H bridge multilevel inverter with the same output quality.

Keywords— Cascaded H-bridge multilevel inverter (CHB), phase shifted modulation, multicarrier pulse-width modulation, total harmonic distortion (THD).

#### INTRODUCTION

Over the past two decades, multilevel inverters have attracted wide interest both in the scientific community and in the industry. The reason for the increased interest is that the multilevel inverters are a viable technology to implement controlled rotational movement in high-power applications. Multilevel inverters include an array of power semiconductors and capacitor voltage sources, the output of which generate voltages with stepped waveforms. The commutation of the switches permits the addition of the capacitor voltages, which reach high voltage at the output, while the power semiconductors must withstand only reduced voltages. Multilevel converters have a lot of advantages to offer in medium- to high-voltage range of applications. These include variable speed motor drives and power system applications. Multilevel converters can synthesize waveforms using more than two voltage levels, small filter components are required and sometimes they can be left out altogether. Disadvantages of multilevel topologies include: high number of semiconductor devices, complex control as a result of the large number of controlled devices, large number of gate drive circuits, several DC voltage sources are required, need to balance voltages across capacitors used in voltage divider circuits. There are different types of multilevel circuits involved. The first topology introduced was the series H-bridge design. This was followed by the diode clamped converter, which utilized a bank of series capacitors. A later invention detailed the flying capacitor design in which the capacitors were floating rather than seriesconnected. Another multilevel design involves parallel connection of inverter phases through inter-phase reactors. In this design, the semiconductors block the entire dc voltage, but share the load current. Several combinational designs have also emerged some involving cascading the fundamental topologies. These designs can create higher power quality for a given number of semiconductor devices than the fundamental topologies alone due to a multiplying effect of the number of levels. The multilevel inverters are mainly classified as diode clamped, Flying capacitor inverter and cascaded multilevel inverter. The cascaded multilevel control method is very easy when compare to another multilevel inverter because it does not require any clamping diode and flying capacitor. In this paper, using a new topology of cascaded H-bridge multilevel inverter for producing nine output voltage levels and for that we are using multicarrier modulation technique. This paper is organized as follows: the inverter's configuration is presented in Section II, the PWM modulation strategy in Section III, analysis of output voltage and harmonics in Section IV, the hardware implementation in Section V and Section VI is the conclusion.

#### II. FIVE LEVEL CASCADED H-BRIDGE MULTILEVEL INVERTER

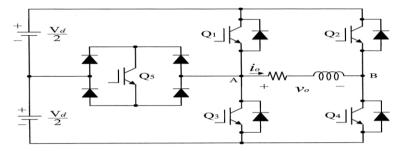

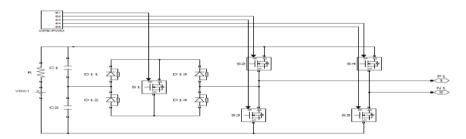

Cascaded multilevel inverter has the advantage of most reliable and to achieve the best fault tolerance owing to its modularity; a feature that enables the inverter to continue operating at lower power levels after cell failure. Modularity also permits the cascaded multilevel inverter to be stacked easily for high power and high voltage applications. The cascaded multilevel inverter typically comprises several identical single phase H-bridge cells cascaded in series at its output side. This configuration is commonly referred to as a cascaded H-bridge (CHB), which can be classified as symmetrical if the dc bus voltages are equal in all the series power cells, or as asymmetrical if otherwise. The main disadvantage of the conventional cascaded H-bridge is that when the voltage level increases, the number of semiconductor switches increases and also the source required increases. In order to overcome this introduced a new topology of cascaded H-bridge. The main advantage of this topology is that the number of switches required is reduced and also the number of sources. Figure 1 shows the new cascaded five levels H-bridge multilevel inverter. It has additional one bidirectional switch connected between the first leg of the H-bridge and the capacitor midpoint, enabling five output voltage levels.

Fig. 1 Five level cascaded H-bridge multilevel inverter

It has five output voltage levels i.e.  $V_{\text{dc}}$ ,  $V_{\text{dc}}$ /2, 0,  $-V_{\text{dc}}$ /2,  $-V_{\text{dc}}$ . For getting the output voltage  $V_{\text{dc}}$ , the switches  $S_1S_4$  need to be turned on. Similarly for output voltage  $V_{\text{dc}}$ /2 switches  $S_5S_4$  need to be turned on, for 0 either  $S_3S_4$  or  $S_1S_2$  need to be turned on; for  $-V_{\text{dc}}$ /2 switches  $S_5S_2$  need to be turned on. The switch combinations are shown in table 1.

TABLE 1 FIVE- LEVEL CASCADED H-BRIDGE OUTPUT VOLTAGE

| S1  | S2  | <b>S</b> 3 | S4  | S5  | $V_{OUT}$                                |

|-----|-----|------------|-----|-----|------------------------------------------|

| ON  | OFF | OFF        | ON  | OFF | $V_{ m dc}$                              |

| OFF | OFF | OFF        | ON  | ON  | $^{1}\!/_{2}$ $\mathrm{V}_{\mathrm{dc}}$ |

| OFF |     | ON         | OFF | OFF |                                          |

| Or  | OFF | Or         | Or  | Or  | 0                                        |

| ON  |     | OFF        | ON  | ON  |                                          |

| OFF | ON  | OFF        | OFF | ON  | $-1/2V_{dc}$                             |

| OFF | ON  | ON         | OFF | OFF | $-V_{ m dc}$                             |

In the circuit shown in fig 1, single H-bridge module can produce five level output voltage. Each inverter module can produce 2E, E, 0, -E, -2E. That means by using two bridges 9 level output voltage is produced. The total output voltage is sum of the outputs of the inverter modules and the nine voltage levels are 4E, 3E, 2E, E, 0, -E, -2E, -3E, -4E. The advantages of this proposed circuit are number of switches are reduced. The cost and complexity are less in this circuit. To synthesize nine output voltage levels, it employs two independent dc voltage sources of 2E which are divided into two input sources E in order to secure an additional dc voltage source of E. The inverter module having a bidirectional switch produces 5-levels of output voltage (- 2E, -E, 0, E, 2E) by controlling of the switches. Since every output terminal of the inverter module is connected in series, the output voltage becomes the sum of the terminal voltages of each inverter. The circuit for nine level cascaded H-bridges is shown in figure 2, the gating signals for the inverter is generated by using multicarrier modulation

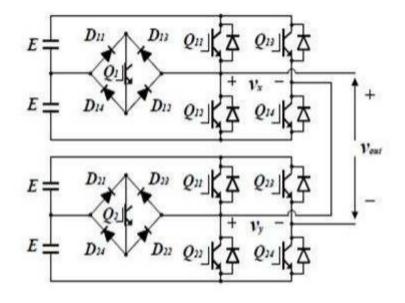

### III. NINE-LEVEL CASCADED H-BRIDGE MULTILEVEL INVERTER

In the circuit shown in figure 1, single H-bridge module can produce five level output voltage. Each inverter module can produce 2E, E, 0, -E, -2E. That means by using two bridges 9 level output voltage is produced. The total output voltage is sum of the outputs of the inverter modules and the nine voltage levels are 4E, 3E, 2E, E, 0, -E, -2E, -3E, -4E. The advantages of this proposed circuit is number of switches are reduced. The cost and complexity are less in this circuit. The inverter module having a bidirectional switch produces 5-levels of output voltage (- 2E, -E, 0, E, 2E) by controlling of the switches. Since every output terminal of the inverter module is connected in series, the output voltage becomes the sum of the terminal voltages of each inverter. The circuit for nine level cascaded h-bridge is shown in figure 2., the gating signals for the inverter is generated by using multicarrier modulation.

Fig. 2 Nine level cascaded H-bridge multilevel inverter

#### IV. PWM MODULATION

In this inverter, the sinusoidal pulse width modulation is going to use. In the Sinusoidal pulse width modulation scheme, as the switch is turned on and off several times during each half-cycle, the width of the pulses is varied to change the output voltage. Lower order harmonics can be eliminated or reduced by selecting the type of modulation for the pulse widths and the number of pulses per half-cycle. Higher order harmonics may increase, but these are of concern because they can be eliminated easily by filters. The SPWM aims at generating a sinusoidal inverter output voltage without low-order harmonics. This is possible if the sampling frequency is high compared to the fundamental output frequency of the inverter. The modulation index, M of the proposed multilevel inverter is defined by,

$$M = \frac{1}{2} \left( V \operatorname{ref} / V \operatorname{cr} \right) \tag{1}$$

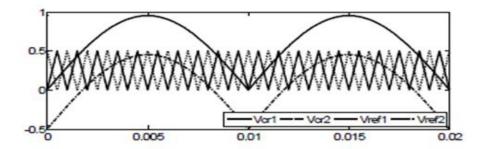

where Vref is the amplitude of the voltage reference and Vcr is the amplitude of the carrier signal. Multicarrier phase-shifted PWM (CPS-PWM) [7] modulation is used to generate the PWM signals. The amplitude and frequency of all triangular carriers are the same as well as the phase shifts between adjacent carriers. Depending on the number of cells, the carrier phase shift for each cell,  $\theta$ cr,n can be obtained from,

$$\theta \text{cr,n} = 2\pi \text{n-1}/\text{Nc}, \text{n} = 1,2,\dots...\text{Nc}$$

(2)

For signal generation in each cell, two voltage references and one carrier signal are used. Vref is defined by

$$Vref = M \sin \omega t$$

$$Vref1 = | Vref$$

$$Vref2 = | Vref - 1/2 |$$

(5)

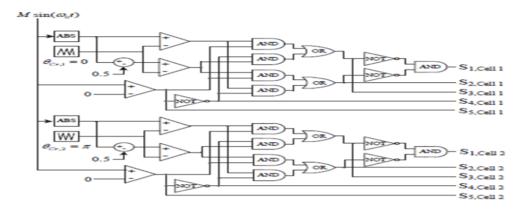

Both references are identical but displaced by an offset equal to the carrier's amplitude which is  $\frac{1}{2}$ . When the voltage reference is between  $0 < vref \le \frac{1}{2}$ , vref I is compared with the triangular carrier and alternately switches SI and SS while maintaining SS in the ON state to produce either  $\frac{1}{2}vcef \le 1$ ,  $vref \le 1$ ,  $vref \le 1$ ,  $vref \le 1$  is used and alternately switches SI and SS while maintaining SS in the ON state to produce either  $\frac{1}{2}vcef \le 0$ , vref I is used for comparison which alternately switches SI and SS while maintaining SS in the ON state to produce either  $\frac{1}{2}vcef \le 0$ , vref I is used for comparison which alternately switches SI and SS while maintaining SS in the ON state to produce either  $\frac{1}{2}vcef \le 0$ , vref I is used for voltage reference between  $\frac{1}{2}vref \le \frac{1}{2}v$ , vref I is compared with the carrier to produce either  $\frac{1}{2}vcef \le 1$  and SS, maintaining SS in the ON state. It is noted that two switches, SS and SS, only operate in each reference half cycle. This implies that both switches operate at the fundamental frequency while the others operate close to the carrier frequency. This allows the dc voltage to be switched at a low frequency so as to reduce the switching losses. Fig. 3 shows the modulation scheme used for the proposed two-cell configuration and Fig. 4 shows a detail block diagram for generating the PWM signals.

Fig 3. Multicarrier phase-shifted PWM for two-cell configuration

Fig 4. PWM signal generation with multicarrier phase-shifted modulation.

## V SIMULATION RESULT

The simulation model was designed using MATLAB/Simulink Software. The gating signals for the inverter are generated by using multicarrier pulse width modulation technique.

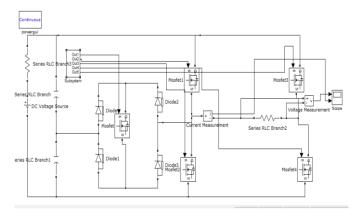

Figure 5 Five level cascaded H-bridge multilevel inverter

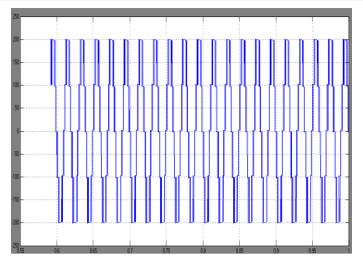

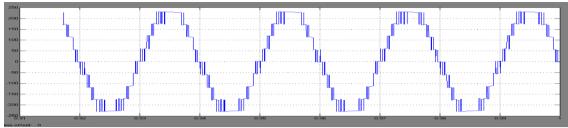

Figure 6 Five level cascaded H-bridge multilevel inverter, output voltage waveform using multicarrier modulation.

© Display FT window

Selected signal

Obsplay FT window

Selected signal: 1 cycles. FFT window (in red): 1 cycles

-200

-200

0 0.002 0.004 0.006 0.008 0.01 0.012 0.014 0.016 0.018 0.02

FFT analysis

Fundamental (50Hz) = 222.1 , THD= 28.83%

Fundamental (50Hz) = 222.1 , THD= 28.83%

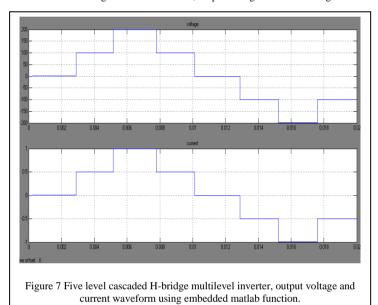

Figure 8. Five level cascaded H-bridge multilevel inverter with multicarrier modulation, THD=28.83%.

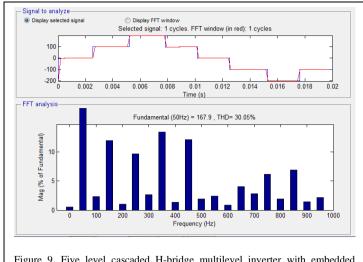

Figure 9. Five level cascaded H-bridge multilevel inverter with embedded matlab function, THD=30.05%.

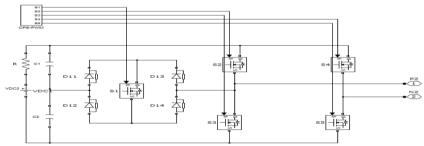

Fig 10. Circuit for Nine level Cascaded H-bidge Multilevel Inverter.

Fig 11. Circuit of cell 1.

Fig 12. Circuit of cell 2

Fig 13. Output voltage waveform.

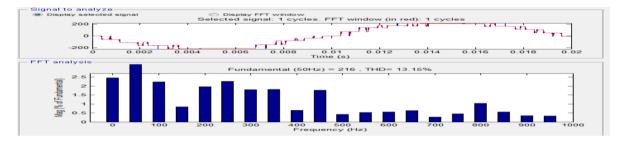

Figure 14. Nine level cascaded H-bridge multilevel inverter with multicarrier modulation, THD=13.15%.

Table 2 Simulation results

|                     | 1       |  |

|---------------------|---------|--|

| Multilevel inverter | THD (%) |  |

| Five level          | 28.83   |  |

| Nine level          | 13.15   |  |

The simulation result shows that THD gets reduced significantly when the output voltage level increases

#### VI CONCLUSION

Multilevel inverters have become an effective and practical solution for increasing power and reducing harmonics of ac waveforms. This paper compares single-phase nine-level Cascaded H-bridge multilevel inverter with five-level cascaded H-bridge multilevel inverter. The simulation of 9-level and 5-level cascaded H-bridge was made. Along with it, its harmonic analysis was done. The simulation results shows that the developed nine-level Cascaded H-bridge Multilevel inverter has many merits such as reduce number of switches, lower EMI, less harmonic distortion and the THD obtained is 13.15%.

### **REFERENCES**

- [1] Nasrudin Abd. Rahim, Mohamad Fathi Mohamad Elias, Wooi Ping Hew, IEEE transaction. Industry Electronics, "Design of filter to reduce harmonic distortion in industrial power system", Vol. 60, No :8, 2943-2956, August 2013.

- [2] J. Selvaraj and N. A. Rahim, "Multilevel Inverter For Grid-Connected PV System Employing Digital PI Controller," *IEEE Trans. Ind. Electron.*, vol. 56, pp. 149-158, 2009.

- [3] Naderi and A. Rahmati, "Phase-Shifted Carrier PWM Technique for General Cascaded Inverters," IEEE Trans. Power Electron., vol. 23, pp. 1257-1269, 2008.

- [4] J. Rodriguez, J.-S. Lai, and F. Z. Peng, —Multilevel inverters: A survey of topologies, controls, and applications, IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [5] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, —A Survey on cascaded multilevel inverters, IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197-2206, July 2010.

- [6] S. J. Park, F. S. Kang, M. H. Lee, and C. U. Kim, —A new single-phase five-level PWM inverter employing a deadbeat control scheme, *IEEE Trans. Power Electron.*, vol. 18, no. 18, pp. 831–843, May 2003.

- [7] N. A. Rahim, and J. Selvaraj, —Multistring five-level inverter with novel PWM control scheme for PV application, IEEE Trans. Ind. Electron., vol. 57, no. 6, pp. 2111-2123, June 2010.