# A Comparative Analysis InP/InGaAs δ Doped based NPN and PNP HBT

M. R. Jena<sup>1\*</sup>

<sup>1</sup>Department of Electronics and Telecommunication

Engineering,

Veer Surendra Sai University of Technology,

Burla, Sambalpur 768018, Odisha, India

A. K. Panda<sup>2</sup>

<sup>2</sup>Department of Electronics and Telecommunication

Engineering,

National Institute of Science and Technology,

Berhampur 761008, Odisha, India

G. N. Dash<sup>3</sup>

<sup>3</sup>Electron Devices Group, School of Physics,

Sambalpur University, Jyoti Vihar, Burla,

Sambalpur768019, Odisha, India

Abstract—In this paper, a comparative study of InP/InGaAs δ doped based npn and pnp HBT is presented using two dimensional (2D) simulation TCAD Silvaco tool. The models are tuned for proper validation with experimental results in 2D simulation environment. The DC, AC and RF of both the devices have performed and compared on the basis of same physical geometry. For npn HBT a maximum of current gain beta (β) 254,  $f_{max}$ =14.34 GHz,  $BV_{CEO}$ =2.72V, and  $V_{CE, offset}$ =20mV where as for pnp HBT a maximum of current gain beta (β) =50 V,  $f_{max}$ =1.8 GHz,  $BV_{CEO}$ =-7.5V, and  $V_{CE,Offset}$ =-0.18V has achieved. The above comparison is also including the effect of spacer and delta doping in the performances of high frequency applications.

Keywords—InP/InGaAs, NPN and PNP Heterojunction bipolar transistors

# I. INTRODUCTION

InP based HBT are among the highest performance III-V semiconductor device to date and are mostly suitable for high speed ICs, wide bandwidth analog, digital and RF application due to its excellent material properties. This type of HBT has several advantages such as large valence band discontinuity, low turn on voltage and compatible with a device having long wavelength and can operate in THz range [1, 2]. In an HBT higher emitter injection efficiency is due to band gap difference and it is important that a significant amount of band gap difference falls across the valence band in case of npn InP/InGaAs HBT. However, in case of pnp, conduction band alignment is suitable to reduce the electron injection into the emitter while a small value of valence band discontinuity help hole injection from the emitter into the base [3]. Composition grading across the depletion region of Emitter-Base junction is usually carried out to reduce the potential spike, but grading is difficult to precisely control and is not applicable to InP/InGaAs HBT [4]. Thus by reducing the potential spike we can lower the turn on voltage which is necessary to reduce the power consumption [1].In this paper potential barrier is lowered by using a thin sheet of charged layer in both npn and pnp HBT known as δ-doped layer. This layer is placed in between the two spacer layer, because as it is moved towards the hetero-interface, the effect of barrier lowering increases [5]. Hence the  $\delta$ -doping is used in npn to increase the hole barrier whereas in pnp to increase the electron barrier. The thin spacer layer in between base and emitter layer reduces the charge storage, thus increases the current gain. However a thicker spacer is undesirable as it increases the electron base transit time which is undesirable for the design of microwave transistor [5]. By using the  $\delta$ doped layer offset voltage is reduced and minimization of offset voltage is important for InP/InGaAs HBT because the breakdown voltage of these HBT is very low [5]. The offset voltage is completely eliminated by matching the turn on voltage of the two junctions. . So, in this paper; The device is properly modelled and validated with the fabrication result of the reference papers for npn HBT [6], for pnp HBT [7].As model is validated for both npn as well as pnp HBT, the DC,AC, and RF characteristics are extracted and compared between them. The detailed device structure of npn HBT and pnp HBT is presented in Section 2, theoretical formulations and model developed is presented in Section 3. Results and Discussions are presented in Section 4 and the paper is finally concluded in Section 5.

# II. DEVICE STRUCTURE

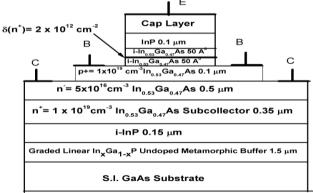

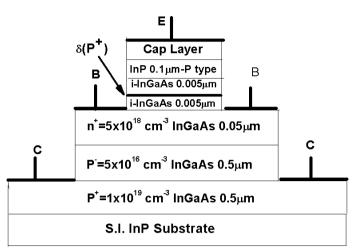

The studied InP/InGaAs δ doped npn HBT consisted of a 1.5 $\mu$ m undoped and linearly graded In<sub>x</sub>Ga<sub>1-x</sub>P (x: 0.52 $\rightarrow$ 1) buffer layer, a 0.15 µm undoped InP layer, a 0.35 µm  $n^+=1\times10^{19}~cm^{-3}~In_{0.53}~Ga_{0.47}As$  subcollector layer, a 0.5  $\mu m~n^-$ = $5\times10^{16}$  cm<sup>-3</sup> In<sub>0.53</sub> Ga<sub>0.47</sub>As collector layer, a 0.1  $\mu$ m  $p^{+}=1\times10^{19}$  cm<sup>-3</sup> In<sub>0.53</sub> Ga<sub>0.47</sub>As base layer, a 50 Å i-In<sub>0.53</sub>  $Ga_{0.47}As$  spacer layer, a  $n^+=2\times10^{12}$  cm<sup>-2</sup>  $\delta$ -doped sheet, a 50 Å i-In<sub>0.53</sub> Ga<sub>0.47</sub>As spacer layer, a 0.1  $\mu$ m n=5×10<sup>17</sup> cm<sup>-3</sup> InP emitter layer, and a 0.3  $\mu m n^{+}=1\times10^{19} cm^{-3} In_{0.53} Ga_{0.47} As cap$ layer. The studied InP/InGaAs δ doped pnp HBT consisted of a 0.5  $\mu$ m p<sup>+</sup>=1 x 10<sup>19</sup>cm<sup>-3</sup> In<sub>0.53</sub> Ga<sub>0.47</sub>As subcollector layer , a 0.5  $\mu$ m p<sup>-</sup> = 5 x 10<sup>16</sup>cm<sup>-3</sup> In<sub>0.53</sub> Ga<sub>0.47</sub>As collector layer, a 500 Å  $n^{+}$ = 5 x 10<sup>18</sup> cm<sup>-3</sup> In<sub>0.53</sub> Ga<sub>0.47</sub>As base layer, a 50 Å i-In<sub>0.53</sub> Ga<sub>0.47</sub>As spacer layer, a p<sup>+</sup>= 2 x  $10^{12}$ cm<sup>-2</sup>  $\delta$  doped sheet, a 50 Å i-  $In_{0.53}$  Ga<sub>0.47</sub>As spacer layer, a 0.1  $\mu$ m p = 5 x 10<sup>17</sup> cm  $^{\text{-}3}$  InP emitter layer, and a 0.3  $\mu m$  p  $^{\text{+}}\text{=}$  1  $x10^{19}$  cm  $^{\text{-}3}$  In $_{0.53}$

Ga<sub>0.47</sub>As cap layer. The structure of npn and pnp HBTs are presented in Fig.1 and Fig.2 respectively.

Use of InGaP buffer in the npn HBT device offers excellent thermal properties, thus a smaller thermal resistance. Each layer performs a specific function and the functional relationship between the layers decides the current gain and speed the device. The semi-insulating substrates have a low dislocation density, which is the key requirement for high speed circuit. Emitter cap layer is added for both cases on top of the emitter to minimize emitter ohmic contact resistance. The emitter, base, collector and subcollector areas of both npn and pnp transistors are A<sub>Emitter</sub>= 5×10<sup>-5</sup>  $cm^2.A_{Base}=15.9\times10^{-5}$ cm<sup>2</sup>. and  $A_{\text{Collector}} = 30 \times 10^{-5} \text{cm}^2$ respectively. The asymmetry of the emitter-base and collector-base junctions introduces an offset voltage. The offset voltage is an undesirable feature since it causes extra power consumption and reduced logic swing under active transistor operation [1] .large offset voltages would be expected due to a difference in turn-on voltage between the emitter-base heterojunction and base-collector homojunction. Smaller turn on voltage between the two junction leads to smaller collector emitter offset voltage. The dipole doping at the InGaAs/InP interface narrows the barrier to the point that electrons should be able to tunnel through the top part of it. In a single heterojunction bipolar transistor (SHBT), there is an energy spike in the emitter side which limits the electron transport from the emitter to the base and results in a higher turn on voltage of the emitter heterojunction. Therefore, elimination of this energy spike from the current transport would reduce the offset voltage significantly. Composition grading in the emitter junction can smooth out this energy spike and thus reduce the emitter turn-on voltage to that of the collector junction. A thicker spacer is not necessary because the effective base width, which includes the spacer thickness in this case, would produce a large electron base transit time which is not desirable in the design of the microwave bipolar transistors. This offset voltage is undesirable in the low bias integrated circuit applications, since it causes increased power dissipation and reduced output voltage swing. It is known that the offset voltage is attributable to the energy spike existing at the conduction band of the emitter junction and is equal to the difference between the turn-on voltages of the emitter and collector junctions.

Fig 1: npn HBT structure

Fig 2: pnp HBT structure

### MODEL SELECTION

In the simulation of the device structure various device model are tunned to get the desired result. Parallel Electric Field Dependence MODEL (FLDMOB) is required to model any type of velocity saturation effect. When parallel electric field dependence are used with energy balance the electric field term is replaced by a function of carrier temperature. FLDMOB should always be specified unless one of the inversion layer mobility models (which incorporate their own dependence on the parallel field) is specified. Bandgap Narrowing- Important in heavily doped regions. This model (BGN) is necessary to correctly model the bipolar Current gain. Auger -Important at high current densities. Auger recombination occurs through a three particle transition whereby a mobile carrier is either captured or emitted. Auger recombination accounting for high level injection effects. AUGER specifies that Auger recombination rate is probed. Concentration Dependent CONMOB- it specifies the concentration dependent mobility. Specifies that doping concentration dependent model to be used for electrons. Shockley-Read-Hall SRH Used to fixed minority carrier lifetime. To simulate the device in breakdown HBT requires selberherr impact ionization (selb) model. It is a temperature dependent parameter. For convergences purpose of absolute current and relative current ir.tol and ix.tol are selected during simulation respectively.

# RESULTS AND DISCUSSION

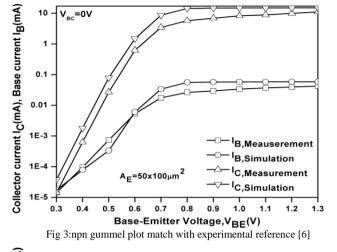

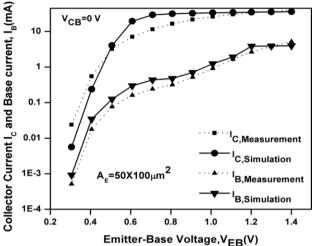

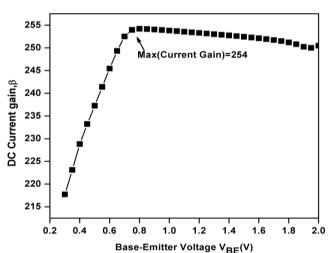

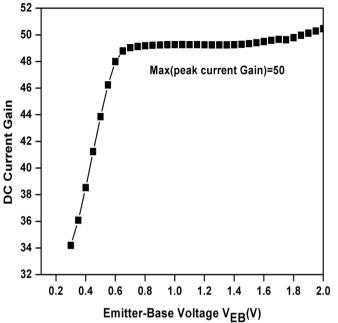

For the InP/InGaAs δ doped npn and pnp HBTs, DC, AC, and RF characteristic are obtained and the results are presented in this section. The gummel plot of both the HBTs is shown in Fig.3 and Fig.4 respectively, which is agreed with the reported fabricated result. The closely agreement of the results shows our accuracy of models. The DC current gain  $\beta$ (beta) for npn and pnp HBT are shown in Fig.5 and Fig.6 respectively. For npn HBT the maximum  $\beta$  is 254 where as in pnp HBT the maximum  $\beta$  is 50. The reason for high gain in npn HBT compared to pnp HBT is due to less number of minority carriers are injected back to the emitter.

Fig 4:pnp gummel plot match with experimental reference [7]

Fig 5: DC current gain (β) of npn HBT

Fig 6: DC current gain (β) of pnp HBT

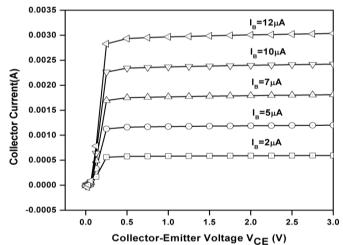

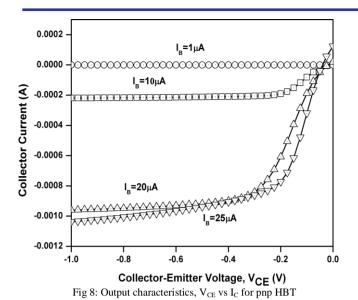

The  $I_C$  versus  $V_{CE}$  curves are shown in Fig.7 and Fig.8 for npn HBT and pnp HBT respectively. Due to convergence problem both have simulated with different base currents. Since for comparison purpose both have included at a common  $I_B\!=\!10\mu A.$  It is clear that for the same base current npn based HBT provides more collector current than the pnp based HBT. Such observation is evident in view of the highest  $\beta$  of npn HBT.

Fig 7: Output characteristics, V<sub>CE</sub> vs I<sub>C</sub> for npn HBT

The Early voltage ( $V_A$ ) is computed from backward extrapolated  $V_{CE}$ -I $_C$  characteristics shown in Fig.7 and Fig.8 respectively. The observed Early voltages for npn and pnp HBTs are -42 V and 7.69 V respectively. The  $V_A$  is the important parameter to measure the output conductance. Higher  $V_A$  is desirable for a HBT for better circuit operation. The  $V_A$  can be expressed as [8]

$$V_A = \frac{\int\limits_0^{W_B} N_{aB}(\mathbf{x}) \, d\mathbf{x}}{N_{aB} W_B \left\{ \frac{\partial W_B}{\partial V_{CB}} \right\}} = \frac{Q_B(0)}{C_{CB}}$$

(1)

where  $Q_B(0)$  is the total base charge at  $V_{CB}$ =0 V and  $C_{CB}$  is the collector base depletion capacitance.

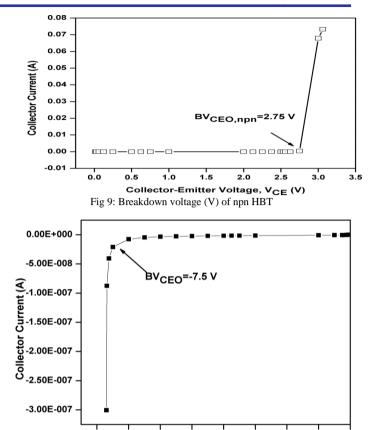

The breakdown voltages in the open base configuration,  $BV_{CEO}$  for npn and pnp HBTs are shown in Fig.9 and Fig.10 respectively. The two HBTs are simulated at a base current of,  $I_B$ =1e-10 A. The reason for choosing such a small base current is to assume that the base terminal is open. The observed breakdown voltages for the HBTs are 2.75 V and -7.5 V for npn and pnp HBTs respectively. The open base configuration  $BV_{CEO}$  can be expressed as [9]

$$BV_{CEO} = \frac{BV_{CBO}}{\sqrt[n]{\beta}} \tag{2}$$

where  $BV_{CBO}$  is the CB breakdown voltage with the emitter left open. The low breakdown voltage for npn HBT can be understood from expression (2), that the high dc current gain of the device is mainly responsible for the same.

Collector-Emitter Voltage, V<sub>CE</sub> (V) Fig 10: Breakdown voltage (V) of pnp HBT

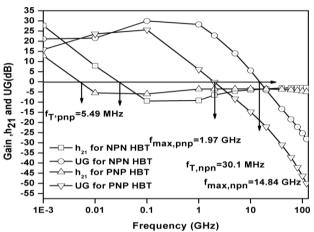

The high frequency performance of the simulated HBTs are characterized by 'S' parameters extracted from the Silvaco tool. The cutoff frequency ( $f_t$ ), defined as the frequency at which the magnitude of short circuit current gain  $\left|h_{21}\right|=1$ , is plotted in Fig. 11. They are recorded to be 30.1 MHz and 5.49 MHz for npn and pnp HBTS respectively. The cut-off frequency ( $f_t$ ) can be expressed as

$$f_t = \frac{1}{2\pi\tau_b} \tag{3}$$

where  $\tau_b$  is the base transit time, defined as the time required to discharge the excess minority carriers in the base through the collector current [10]

$$\tau_b = \frac{W_B^2}{D_{nB}} \tag{4}$$

where,  $W_B^2$  is the width of base region,  $D_{nB}$  is the diffusion coefficient of carrier in the base region. The  $D_n$  value of electron is higher than that of hole [11]. Thus it is clear that npn HBT having lower  $\tau_b$  than that of pnp HBT. Hence higher  $f_t$  is observed in the npn HBT .

$f_{max}$  is the maximum oscillation frequency of a device and it is determined with the condition Massion's Unilateral Power Gain,  $\left| MUG \right| = 1$ , using unit-gain-point method. The fmax of the both HBTs are presented in Fig 11.. The  $f_{max}$  of pnp and npn HBTs are found to be 1.97 GHz and

14.84 GHz respectively. The maximum oscillation frequency is expressed as [10]

$$f_{\text{max}} = \sqrt{\frac{f_t}{8\pi r_b c_{ic}}} \tag{5}$$

where  $f_t$  is cut-off frequency,  $r_b$  the base resistance, and  $c_{jc}$  is the collector junction capacitance.

Fig 11:  $f_T$ ,  $f_{max}$  of both the HBTs

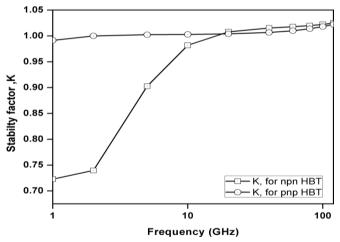

The stability factor, K, measures whether a transistor will be unconditionally stable for arbitrary passive loads [12]. The Rollett stability factor can be expressed in terms of S-parameters as [10]:

$$K = \frac{1 - \left| s_{11} \right|^2 - \left| s_{22} \right|^2 + \left| \Delta s \right|^2}{2 \left| s_{12} \cdot s_{21} \right|} \tag{6}$$

where  $\Delta s=s_{11}s_{22}-s_{12}s_{21}$ . The stability factors of all the transistors are shown in Fig 12. It is observed that the stability issue of pnp HBT is better than the npn HBT as K >1.

Fig 12: Stability factor, K of both the HBT

## V. CONCLUSIONS

InP technology is preferred over other technologies for high linearity low noise power amplifiers because of their higher integration, higher frequency, higher power, higher power

efficiency, lower noise, and lower cost. The future is bright for structures and devices based on InP material system because of their higher integration. In the present work we use Silvaco TCAD 2D Simulator to extract the various value of device parameter. The estimated value of the current gain in this paper agrees well with the measured value reported by fabrication. HBT based on InP/InGaAs are attractive for optical and high speed application because of high electron mobility in the base region. In addition the substrate has higher thermal conductivity and lower surface recombination velocity. At the same time InP buffer is advantageous in reducing thermal resistance. Excellent current gain and high frequency of operation makes the InP based HBT a popular candidate for hand-held wireless area. In addition low turn-on voltage consequently makes the device highly preferable for low power application. Addition of spacer and  $\delta$ -doped layer lowers the offset voltage while increasing the gain. Better performance provides a great promise to the device for high speed and low power application. Moreover the most extensive FOM analysis for these devices such as current gain, I-V behavior, maximum cutoff frequency and breakdown voltage for these devices have been carried out. From the various figure of merits we can easily find that npn HBT exhibit better performances as compared to pnp HBT.

### REFERENCES

- Jung-Hui Tsai\*, Yu-Jui Chu," Influence of spacer layer on InP/InGaAs δ doped heterojunction bipolar transistors", Materials Chemistry and Physics 91 (2005) 431–436.

- [2] Johann C. Rode, Han-Wei Chiang, Prateek Choudhary, Vibhor Jain, Brian J. Thibeault, William J. Mitchell, Mark J. W. Rodwell, Miguel Urteaga, Dmitri Loubychev, Andrew Snyder, Ying Wu, Joel M. Fastenau, and Amy W. K. Liu," Indium Phosphide Heterobipolar Transistor Technology Beyond 1-THz Bandwidth" IEEE Transactions on Electron Devices, This article has been accepted for inclusion in a future issue of this journal. pp 1-7, 2015.

- [3] J. H. Tsai <sup>a</sup>^, W. Ch. Liu<sup>b</sup>, D. F. Guo<sup>c</sup>, Y. Ch. Kang<sup>a</sup>, Sh. Y. Chiu<sup>d</sup>, and W. Sh. Lour<sup>db</sup> Electrical Properties of the InP/InGaAs *pnp* Heterostructure–Emitter Bipolar Transistor" Semiconductors, 2008, Vol. 42, No. 3, pp. 346–349.

- [4] H. R. Chen, C. H. Huang, C. Y. Chang, C. P. Lee, K. L. Tsai, and J. S. Tsang," Heterojunction Bipolar Transistors with Emitter Barrier Lowered by &Doping", IEEE Electron Device Le'iters, vol. 15, NO. 8, AUGUST 1994.

- [5] H. R. Chen, C. P. Lee, C. H. Huang, C. Y. Chang, J. S. Tsang, and K. L. Tsai," The Application of Delta-Doping in Heterojunction Bipolar Transistors" EDMs'94pp-7-3-9 to 7-3-11.

- [6] Jung-Hui Tsai<sup>a\*</sup>, Wen-Shiung Lour<sup>b</sup>, Yi-Ting Chao<sup>a</sup>, Sheng-Shiun Ye<sup>a</sup>, Yung-Chun Ma<sup>a</sup>, Jia-Cing Jhou<sup>a</sup>, You-Ren Wu<sup>a</sup>, Jhih-Jhong Ou-Yang a," An InP/InGaAs metamorphic δ-doped heterojunction bipolar transistor with high current gain and low offset voltage" Thin Solid Films 521 (2012) 172–175.

- [7] J.-H. Tsaia, K.-P. Zhu, Y.-C. Chu, and S.-Y. Chiu, High-performance InP/InGaAs pnp δ-doped heterojunction bipolar transistor" Eur. Phys. J. Appl. Phys. 30, 167–169 (2005).

- [8] John D. Cressler, Guofu Niu, Silicon-Germanium Heterojunction Bipolar Transistors, Artech House, Boston, 2003

- [9] Donald A. Neaman, Semiconductor Physics and Devices, Tata McGraw-Hill Publishing, India, 2007.

- [10] William Liu, Handbook of III-V Heterojunction Bipolar Transistors, John Wiley & Sons, UK, 1998.

- [11] Web resource: www.ioffe.ru/SVA/NSM/Semicond/.

- [12] Steve C. Cripps, RF Power Amplifiers for Wireless Communications, Artech House, Boston, 2006.